Bit net address (rom id), Authentication – Rainbow Electronics DS2778 User Manual

Page 32

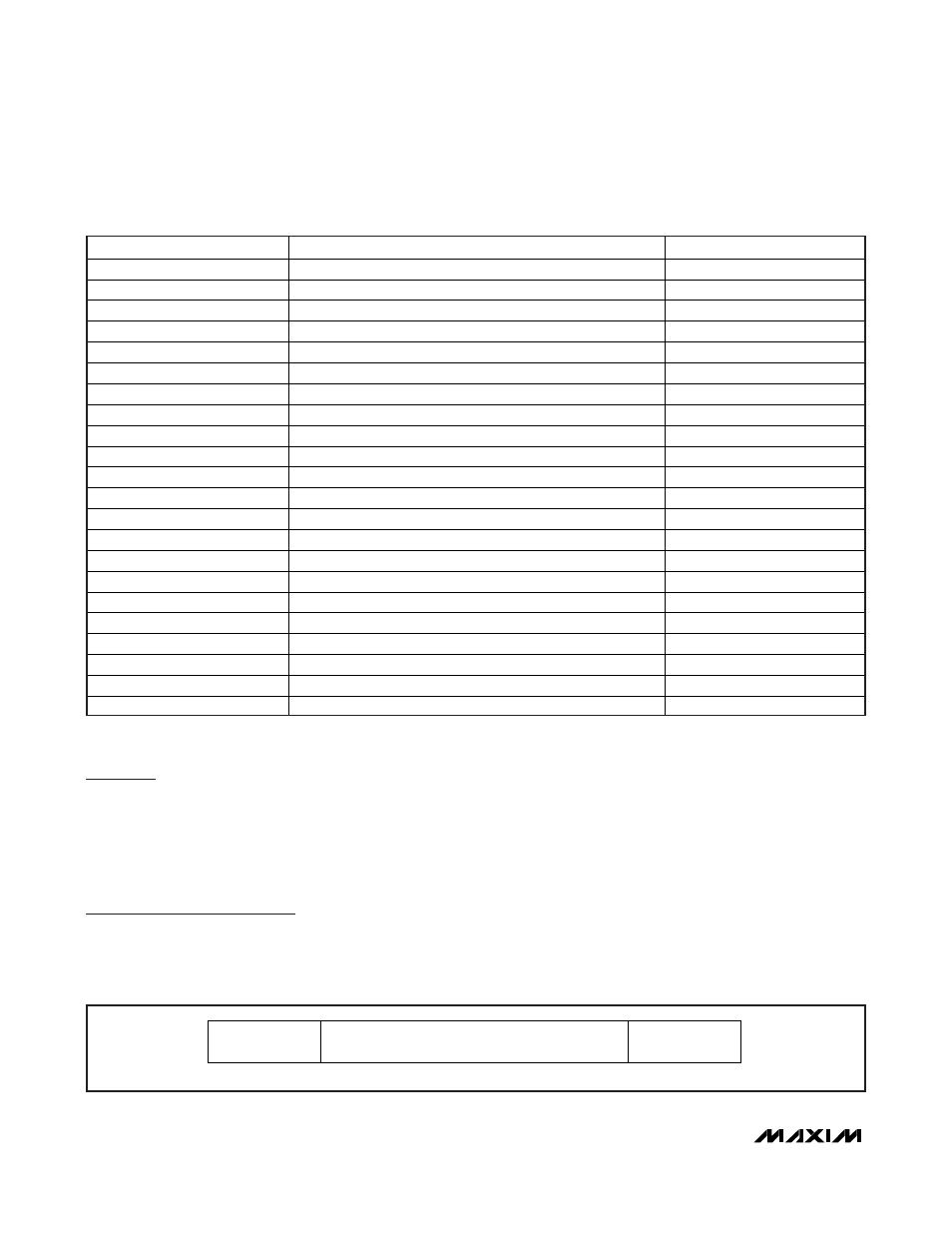

64-Bit Net Address (ROM ID)

Each DS2775–DS2778 has a unique, factory-pro-

grammed ROM ID that is 64 bits. The first 8 bits of the

net address are the product family code (32h). The next

48 bits are a unique serial number. The last 8 bits are a

cyclic redundancy check (CRC) of the first 56 bits (see

Figure 22).

Authentication

The DS2776/DS2778 have an authentication feature

that is performed using a FIPS 180-compliant SHA-1

one-way hash algorithm on a 512-bit message block.

The message block consists of a 64-bit secret, a 64-bit

challenge, and 384 bits of constant data. Optionally,

the 64-bit net address replaces 64 of the 384 bits of

constant data used in the hash operation. Contact

Maxim for details of the message block organization.

The host and the DS2776/DS2778 both calculate the

result based on the mutually known secret. The result

data, known as the message authentication code

(MAC) or message digest, is returned by the

DS2776/DS2778 for comparison to the host’s result.

Note that the secret is never transmitted on the bus and

thus cannot be captured by observing bus traffic. Each

authentication attempt is initiated by the host system by

providing a 64-bit random challenge through the Write

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

32

______________________________________________________________________________________

ADDRESS (HEX)

DESCRIPTION

READ/WRITE

13h

Accumulated Current Register LSB - 2

R

14h Age

Scalar

Register

R/W*

15h

Special Feature Register

R/W

16h Full

Register

MSB

R

17h Full

Register

LSB

R

18h Active-Empty

Register

MSB

R

19h Active-Empty

Register

LSB

R

1Ah Standby-Empty

Register

MSB

R

1Bh Standby-Empty

Register

LSB

R

1Ch

Voltage Register MSB, V

IN2

- V

IN1

R

1Dh

Voltage Register LSB, V

IN2

- V

IN1

R

1Eh Cycle

Counter

Register

R/W*

1Fh EEPROM

Register

R/W

20h to 2Fh

User EEPROM Register, Lockable, Block 0

R/W

30h to 5Fh

Reserved

—

60h to 80h

Parameter EEPROM Register, Lockable, Block 1

R/W

81h to AFh

Reserved

—

B0h

Factory Gain RSGAIN Register MSB

R

B1h

Factory Gain RSGAIN Register LSB

R

B2h to FDh

Reserved

—

FEh 2-Wire

Command

Register

W

FFh Reserved

—

Table 9. Memory Map (continued)

*

Register value is automatically saved to EEPROM during active-mode operation and recalled from EEPROM on power-up.

8-BIT CRC

48-BIT SERIAL NUMBER

8-BIT FAMILY

CODE (32h)

MSb

LSb

Figure 22. 1-Wire Net Address Format (ROM ID)