12 integration time and clock jitter, 13 power management, 14 nap mode – Rainbow Electronics AT77C102B User Manual

Page 14

14

5364A–BIOM–09/05

AT77C102B

For code 0 and 15, the absolute value is a minimum (saturation).

When the image contrast becomes faint because of a low temperature difference between the

finger and the sensor, it is recommended to use the temperature stabilization circuitry to

increase the temperature by two codes (that is from 8 to 10), so as to obtain a sensor increase of

at least >1.4 Kelvin. This enables enough contrast to obtain a proper fingerprint reconstruction.

3.12

Integration Time and Clock Jitter

The AT77C102B is not very sensitive to clock jitters (clock variations). The most important

requirement is a regular integration time that ensures the frame reading rate is also as regular as

possible, so as to obtain consistent fingerprint slices.

If the integration time is not regular, the contrast can vary from one frame to another.

Note that it is possible to introduce some waiting time between each set of 1124 clock pulses,

but the overall time of one frame read must be regular. This waiting time is generally the time

needed by the processor to perform some calculation over the frame (to detect the finger, for

instance).

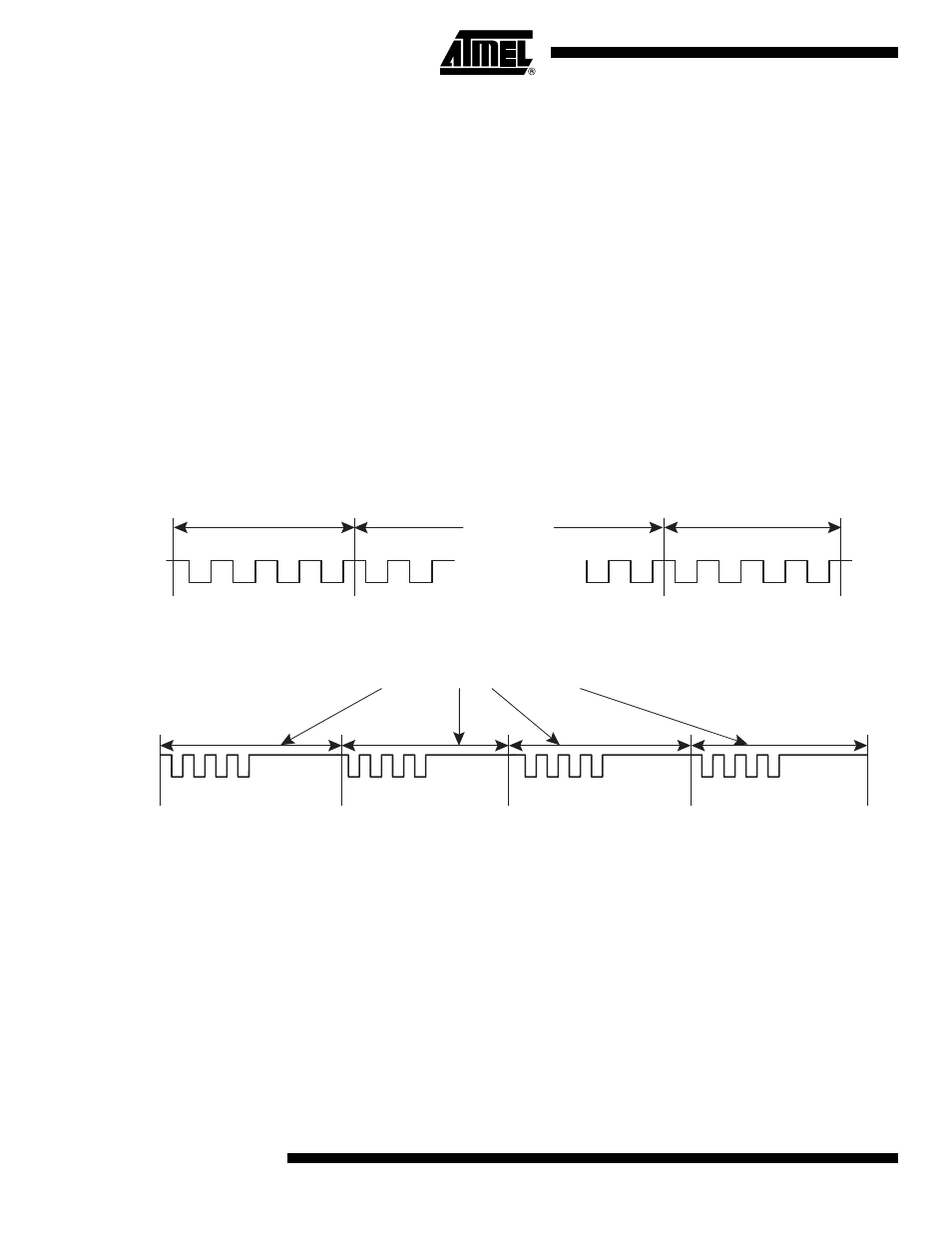

Figure 3-9.

Read One Frame

Figure 3-10. Regular Integration Time

3.13

Power Management

3.14

Nap Mode

Several strategies are possible to reduce power consumption when the device is not in use.

The simplest and most efficient is to cut the power supply using external means.

A nap mode is also implemented in the AT77C102B. To activate this nap mode, you must:

1.

Set the reset RST pin to high. By doing this, all analog sections of the device are inter-

nally powered down.

2.

Set the clock PCLK pin to high (or low), thus stopping the entire digital section.

3.

Set the TPE pin to low to stop the temperature stabilization feature.

4.

Set the Output Enable OE pin to high, so that the output is forced in HiZ.

Clock PCLK

Reset RST is low

1

2

3

4

5

6

1124

1123

1122

1121

1120

1119

Column 1

Column 2

Column 280

Dummy Column 281

Pixels 1 & 2 3 & 4 5 & 6 7 & 8 1 & 2 3 & 4

7 & 8

DB1 DB2 DB3 DB4

Clock PCLK

REGULAR INTEGRATION TIME

Frame n

1124 pulses

Frame n+1

1124 pulses

Frame n+2

1124 pulses

Frame n+3

1124 pulses