5 reading the frames, 6 read one byte/output enable, 7 power supply noise – Rainbow Electronics AT77C102B User Manual

Page 12: 8 video output, 9 pixel order

12

5364A–BIOM–09/05

AT77C102B

3.5

Reading the Frames

A frame consists of 280 true columns plus one dummy column of eight pixels. As two pixels are

output at a time, a system must send 281 x 4 = 1124 clock pulses to read one frame.

Reset must be low when reading the frames.

3.6

Read One Byte/Output Enable

The clock is taken into account on its falling edge and data is output on its rising edge.

For each clock pulse, after the start sequence, a new byte is output on the Do0-3 and De0-3

pins. This byte contains two pixels: 4-bit on Do0-3 (odd pixels), 4-bit on De0-3 (even pixels).

To output the data, the output enable (OE) pin must be low. When OE is high, the Do0-3 and

De0-3 pins are in high-impedance state. This facilitates an easy connection to a microprocessor

bus without additional circuitry since the data output can be enabled using a chip select signal.

Note that the AT77C102B always sends data: there is no data exchange to switch to read/write

mode.

3.7

Power Supply Noise

IMPORTANT: When a falling edge is applied on OE (that is when the Output Enable becomes

active), then some current is drained from the power supply to drive the eight outputs, producing

some noise. It is important to avoid such noise just after the PCLK clock’s falling edge, when the

pixels’ information is evaluated: the timing diagram (

) and time T

NOOE

define the inter-

val time when the power supply must be as quiet as possible.

3.8

Video Output

An analog signal is also available on pins AVE and AVO. Note that video output is available one

clock pulse before the corresponding digital output (one clock pipe-line delay for the analog to

digital conversion).

3.9

Pixel Order

After a reset, pixel 1 is located on the upper left corner, looking at the chip with bond pads to the

right. For each column of eight pixels, pixels 1, 3, 5 and 7 are output on odd data Do0-3 pins,

and pixels 2, 4, 6 and 8 are output on even data De0-3 pins. The Most Significant Bit (MSB) is bit

3, and the Least Significant Bit is bit 0.

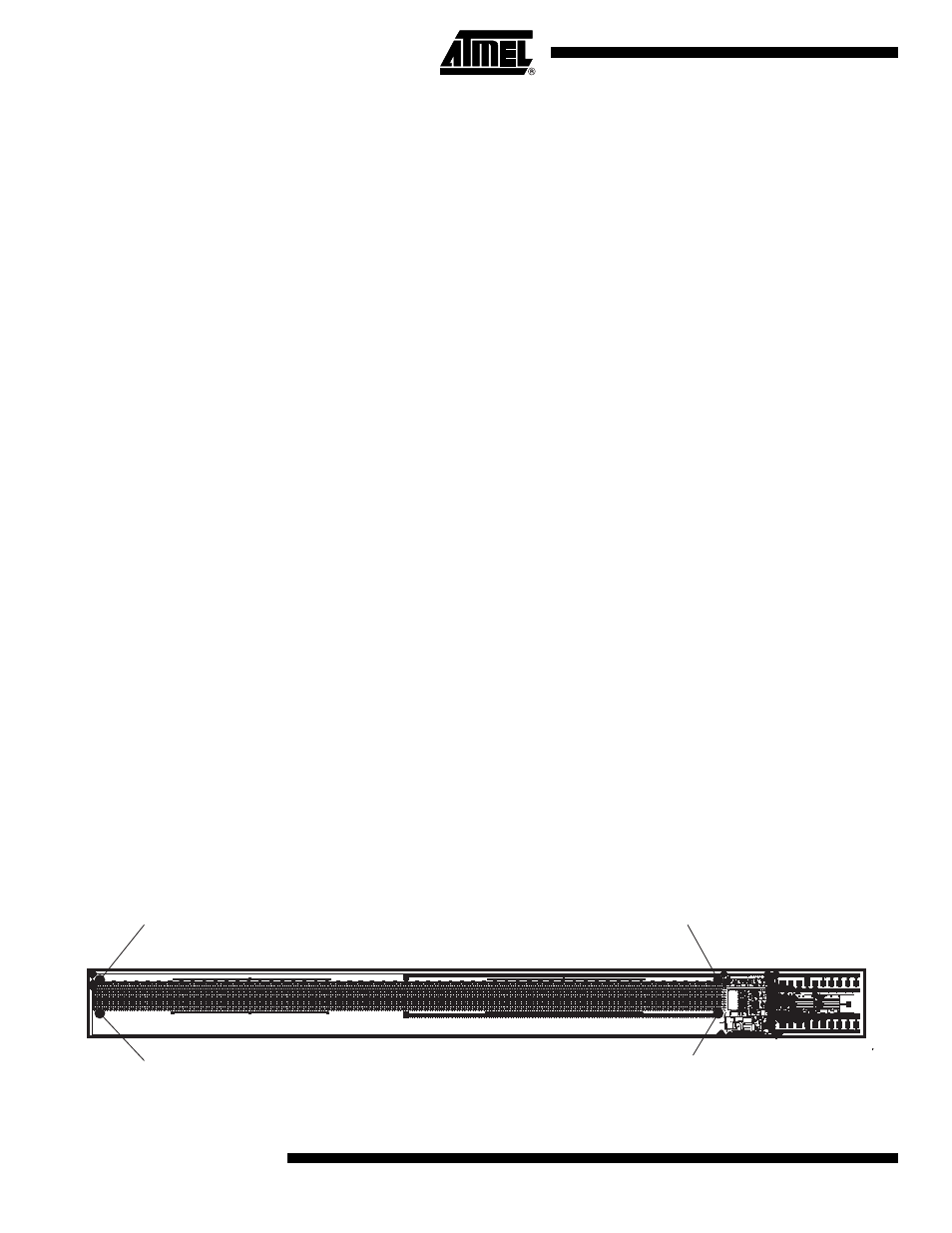

Figure 3-8.

Pixel Order

B ond pads

Pixel #1 (1,1)

Pixel #2233 (280,1)

Pixel #8 (1,8)

Pixel #2240 (280,8)