Test access port (tap) – Rainbow Electronics MAX16071 User Manual

Page 38

12-Channel/8-Channel, Flash-Configurable System

Managers with Nonvolatile Fault Registers

MAX16070/MAX16071

38 _____________________________________________________________________________________

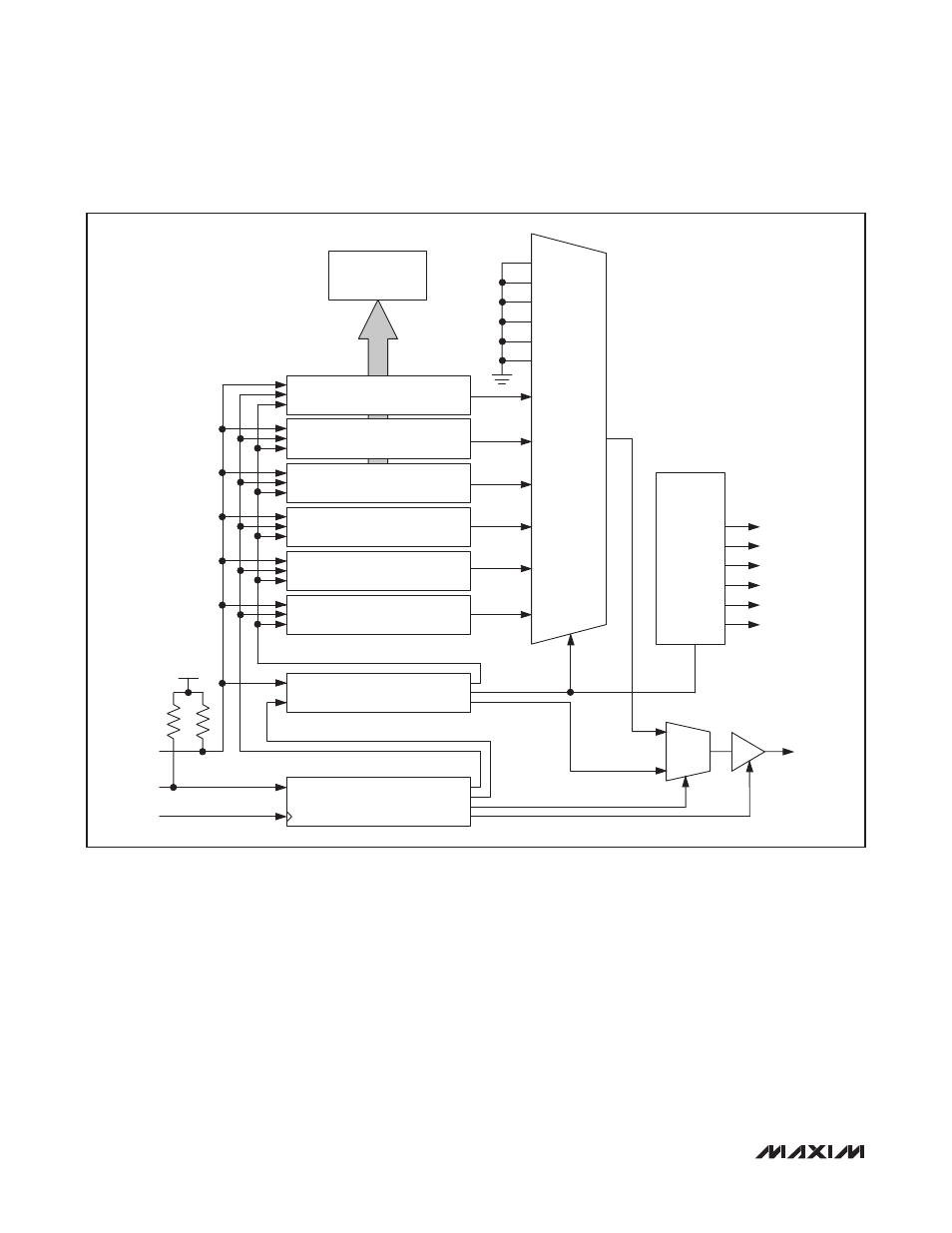

Figure

12. JTAG Block Diagram

Test Access Port (TAP)

Controller State Machine

The TAP controller is a finite state machine that responds

to the logic level at TMS on the rising edge of TCK. See

Figure 13 for a diagram of the finite state machine. The

possible states are described in the following:

Test-Logic-Reset: At power-up, the TAP controller

is in the test-logic-reset state. The instruction register

contains the IDCODE instruction. All system logic of the

device operates normally. This state can be reached

from any state by driving TMS high for five clock cycles.

Run-Test/Idle: The run-test/idle state is used between

scan operations or during specific tests. The instruction

register and test data registers remain idle.

Select-DR-Scan: All test data registers retain their previ-

ous state. With TMS low, a rising edge of TCK moves the

controller into the capture-DR state and initiates a scan

sequence. TMS high during a rising edge on TCK moves

the controller to the select-IR-scan state.

Capture-DR: Data can be parallel-loaded into the test

data registers selected by the current instruction. If the

instruction does not call for a parallel load or the selected

test data register does not allow parallel loads, the test

TEST ACCESS PORT

(TAP) CONTROLLER

INSTRUCTION REGISTER

[LENGTH = 5 BITS]

BYPASS REGISTER

[LENGTH = 1 BIT]

IDENTIFICATION REGISTER

[LENGTH = 32 BITS]

USER CODE REGISTER

[LENGTH = 32 BITS]

MEMORY ADDRESS REGISTER

[LENGTH = 8 BITS]

MEMORY READ REGISTER

[LENGTH = 8 BITS]

MEMORY WRITE REGISTER

[LENGTH = 8 BITS]

11111

00000

00011

00100

00101

00110

00111

MUX 2

TDO

TDI

TMS

TCK

01000

REGISTERS

AND FLASH

01001

01010

01011

01100

MUX 1

00111

01000

01100

01011

01010

01001

REBOOT

SAVE

RSTUSRFLSH

RSTFLSHADD

SETUSRFLSH

SETFLSHADD

COMMAND

DECODER

R

PU

V

DB