Rainbow Electronics MAX16071 User Manual

Page 26

12-Channel/8-Channel, Flash-Configurable System

Managers with Nonvolatile Fault Registers

MAX16070/MAX16071

26 _____________________________________________________________________________________

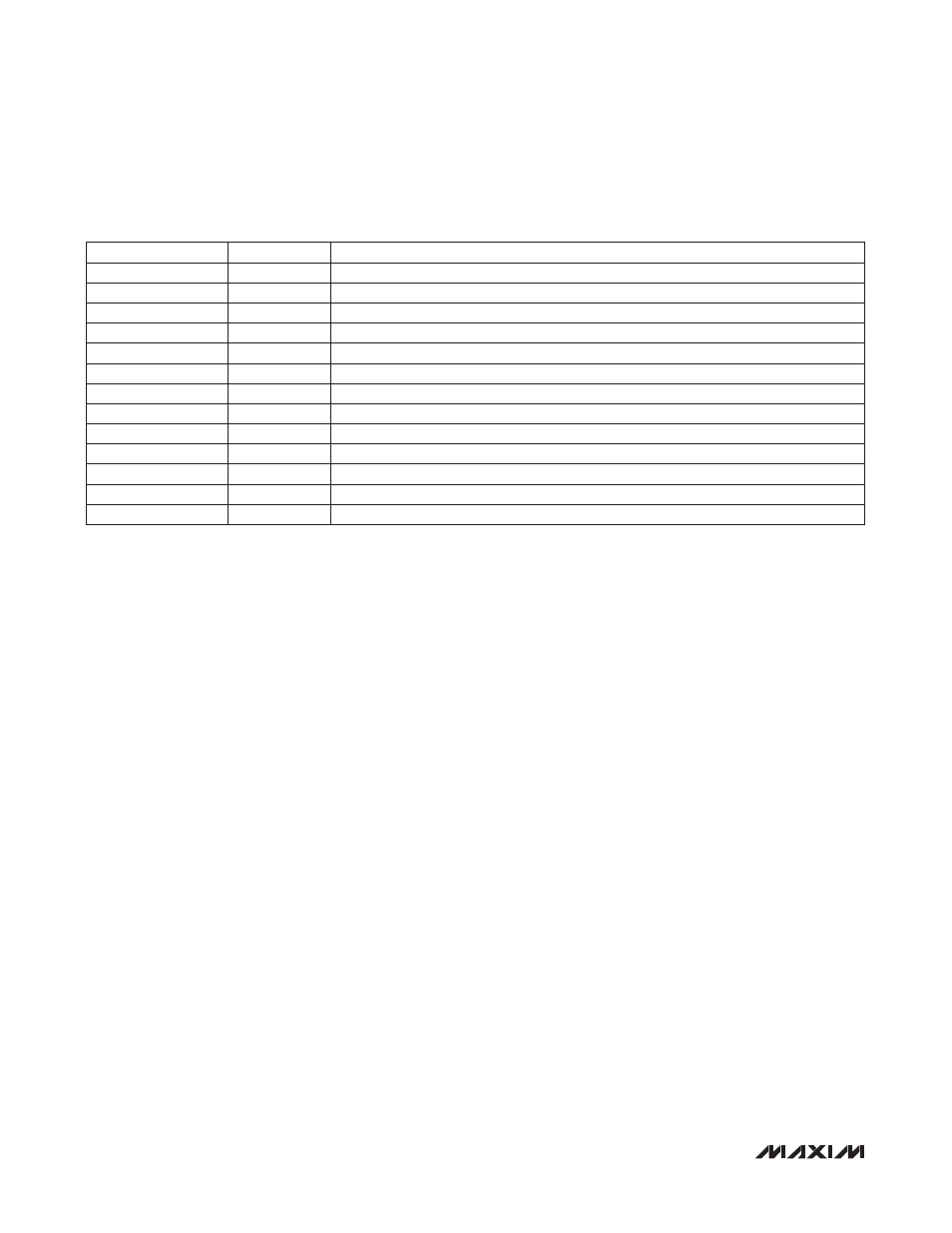

Table

15. Nonvolatile Fault Log Registers (continued)

Reset Output

The reset output, RESET, indicates the status of the moni-

tored inputs.

During normal monitoring, RESET can be configured to

assert when any combination of MON_ inputs violates

configurable combinations of thresholds: undervoltage,

overvoltage, or early warning. Select the combination of

thresholds using r3Bh[1:0], and select the combination

of MON_ inputs using rCh[7:1] and r3Dh[4:0]. Note that

MON_ inputs configured as critical faults will always cause

RESET to assert regardless of these configuration bits.

RESET can be configured as push-pull or open drain

using r3Bh[3], and active-high or active-low using

r3Bh[2]. Select the reset timeout by loading a value from

Table 16 into r3Bh[7:4]. RESET can be forced to assert

by writing a ‘1’ into r3Ch[0]. RESET remains asserted

for the reset timeout period after a ‘0’ is written into

r3Ch[0]. See Table 16. The current state of RESET can

be checked by reading r20h[0].

Watchdog Timer

The watchdog timer operates together with or indepen-

dently of the MAX16070/MAX16071. When operating in

dependent mode, the watchdog is not activated until EN

goes high and RESET is deasserted. When operating in

independent mode, the watchdog timer activates imme-

diately after V

CC

exceeds the UVLO threshold and the

boot phase is complete. Set r73h[4] to ‘0’ to configure

the watchdog in dependent mode. Set r73h[4] to ‘1’ to

configure the watchdog in independent mode. See Table

17 for more information on configuring the watchdog

timer in dependent or independent mode.

Dependent Watchdog Timer Operation

Use the watchdog timer to monitor FP activity in two

modes. Flexible timeout architecture provides an adjust-

able watchdog startup delay of up to 300s, allow-

ing complicated systems to complete lengthy boot-up

routines. An adjustable watchdog timeout allows the

supervisor to provide quick alerts when processor activ-

ity fails. After each reset event (V

CC

drops below UVLO

then returns above UVLO, software reboot, manual reset

(MR), EN input going low then high, or watchdog reset),

the watchdog startup delay provides an extended time

for the system to power up and fully initialize all FP and

system components before assuming responsibility for

routine watchdog updates. Set r76h[6:4] to a value other

than ‘000’ to enable the watchdog startup delay. Set

r76h[6:4] to ‘000’ to disable the watchdog startup delay.

FLASH ADDRESS

BIT RANGE

DESCRIPTION

203h

[7:0]

MON1 ADC output

204h

[7:0]

MON2 ADC output

205h

[7:0]

MON3 ADC output

206h

[7:0]

MON4 ADC output

207h

[7:0]

MON5 ADC output

208h

[7:0]

MON6 ADC output

209h

[7:0]

MON7 ADC output

20Ah

[7:0]

MON8 ADC output

20Bh

[7:0]

MON9 ADC output

20Ch

[7:0]

MON10 ADC output

20Dh

[7:0]

MON11 ADC output

20Eh

[7:0]

MON12 ADC output

20Fh

[7:0]

Current-sense ADC output