Rainbow Electronics MAX16071 User Manual

Page 33

12-Channel/8-Channel, Flash-Configurable System

Managers with Nonvolatile Fault Registers

MAX16070/MAX16071

______________________________________________________________________________________ 33

Packet Error Checking (PEC)

The MAX16070/MAX16071 feature a PEC mode that is

useful for improving the reliability of the communication

bus by detecting bit errors. By enabling PEC, an extra

CRC-8 error check byte is added in the data string dur-

ing each read and/or write sequence. Enable PEC by

writing a ‘1’ to r8Bh[7].

The CRC-8 byte is calculated using the polynomial

C = X

8

+ X

2

+ X + 1

The PEC calculation includes all bytes in the transmis-

sion, including address, command, and data. The PEC

calculation does not include ACK, NACK, START, STOP,

or REPEATED START.

Command Codes

The MAX16070/MAX16071 use eight command codes

for block read, block write, and other commands. See

Table 21 for a list of command codes.

To initiate a software reboot, send A7h using the send byte

format. A software-initiated reboot is functionally the same

as a hardware-initiated power-on reset. During boot-up,

flash configuration data in the range of 230h to 28Ch is

copied to r30h to r8Ch registers in the default page.

Send command code A8h to trigger a fault store to flash.

Configure the Critical Fault Log Control register (6Dh) to

store ADC conversion results and/or fault flags.

While in the flash page, send command code A9h to

access the flash page (addresses from 200h to 28Fh).

Once command code A9h has been sent, all addresses

are recognized as flash addresses only. Send command

code AAh to return to the default page (addresses from

000h to 0FFh). Send command code ABh to access

the user flash-page (addresses from 300h to 3A4h and

3ADh–3ffh), and send command code ACh to return to

the flash page.

Restrictions When Writing to Flash

Flash must be written to 8 bytes at a time. The initial

address must be aligned to 8-byte boundaries—the

three LSBs of the initial address must be ‘000.’ Write the

8 bytes using a single block-write command or using 8

successive Write Byte commands.

Send Byte

The send byte protocol allows the master device to send

one byte of data to the slave device (see Figure 11). The

send byte presets a register pointer address for a subse-

quent read or write. The slave sends a NACK instead of

an ACK if the master tries to send a memory address or

command code that is not allowed. If the master sends

A5h or A6h, the data is ACK, because this could be the

start of the write block or read block. If the master sends

a STOP condition before the slave asserts an ACK, the

internal address pointer does not change. If the master

sends A7h, this signifies a software reboot. The send

byte procedure is the following:

1) The master sends a START condition.

2) The master sends the 7-bit slave address and a write

bit (low).

3) The addressed slave asserts an ACK on SDA.

4) The master sends an 8-bit memory address or com-

mand code.

5) The addressed slave asserts an ACK (or NACK) on SDA.

6) The master sends a STOP condition.

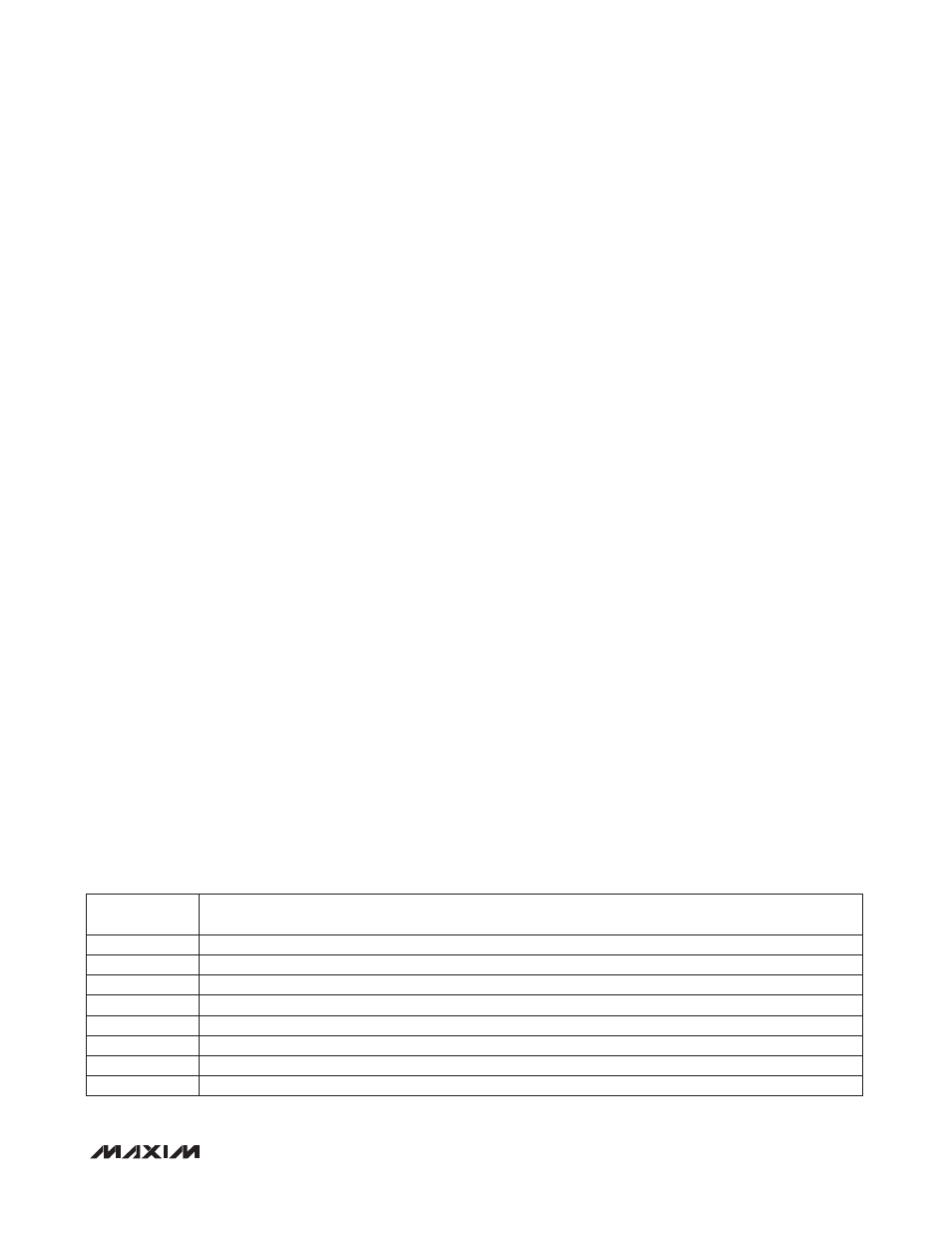

Table

21. Command Codes

COMMAND

CODE

ACTION

A5h

Block write

A6h

Block read

A7h

Reboot flash in register file

A8h

Trigger emergency save to flash

A9h

Flash page access ON

AAh

Flash page access OFF

ABh

User flash access ON (must be in flash page already)

ACh

User flash access OFF (return to flash page)