Detailed description, Table 1. software enable configurations – Rainbow Electronics MAX16068 User Manual

Page 10

10 _____________________________________________________________________________________

MAX16068

6-Channel, Flash-Configurable System Manager

with Nonvolatile Fault Registers

Detailed Description

The MAX16068 monitors up to six system power sup-

plies. The monitoring phase begins after boot-up if EN is

high and the software enable bit is set to ‘1’. An internal

multiplexer cycles through each MON_ input. At each

multiplexer stop, the 10-bit ADC converts the monitored

analog voltage to a digital result and stores the result in

a register. Each time a conversion cycle (5Fs, max) com-

pletes, internal logic circuitry compares the conversion

results to the overvoltage and undervoltage thresholds

stored in memory. When a result violates a programmed

threshold, the conversion can be configured to generate

a fault. GPIO_ can be programmed to assert on combi-

nations of faults. Additionally, faults can be configured to

trigger the nonvolatile fault logger, which writes all fault

information automatically to the flash and write-protects

the data to prevent accidental erasure.

The MAX16068 contains both SMBus and JTAG serial

interfaces for accessing registers and flash. Use only

one interface at any given time. For more information

on how to access the internal memory through these

interfaces, see the SMBus-Compatible Serial Interface

and JTAG Serial Interface sections. The memory map

is divided into three pages with access controlled by

special SMBus and JTAG commands.

The factory-default values at POR (power-on reset) for all

RAM registers are ‘0’s. POR occurs when V

CC

reaches

the undervoltage-lockout threshold (UVLO) of 2.7V

(max). At POR, the device begins a boot-up sequence.

During the boot-up sequence, all monitored inputs are

masked from initiating faults and flash contents are

copied to the respective register locations. During boot-

up, the MAX16068 is not accessible through the serial

interface. The boot-up sequence takes up to 150Fs, after

which the device is ready for normal operation. RESET

is asserted low up to the boot-up phase after which it

assumes its programmed active state. RESET remains

active for its programmed timeout period once all moni-

tored channels are within their respective thresholds. Up

to the boot-up phase, the GPIO_s are high impedance.

Power

Apply 2.8V to 14V to V

CC

to power the MAX16068.

Bypass V

CC

to ground with a 10FF capacitor. Two inter-

nal voltage regulators, ABP and DBP, supply power to

the analog and digital circuitry within the device. For

operation at 3.6V or lower, disable the regulators by con-

necting ABP and DBP to V

CC

.

ABP is a 3.0V (typ) voltage regulator that powers the inter-

nal analog circuitry. Bypass ABP to GND with a 1FF ceram-

ic capacitor installed as close as possible to the device.

DBP is an internal 3.0V (typ) voltage regulator. DBP

powers flash and digital circuitry. All push-pull outputs

refer to DBP. DBP supplies the input voltage to the inter-

nal charge pump when the programmable outputs are

configured as charge-pump outputs. Bypass the DBP

output to GND with a 1FF ceramic capacitor installed as

close as possible to the device.

Do not power external circuitry from ABP or DBP.

Enable Input (EN)

To enable monitoring, the voltage at EN must be above

1.24V (typ) and the software enable bit in r73h[0] must

be set to ‘1.’ To disable monitoring, either pull EN

below 1.215V (typ) or set the software enable bit to ‘0.’

See Table 1 for the software enable bit configurations.

Connect EN to ABP if not used.

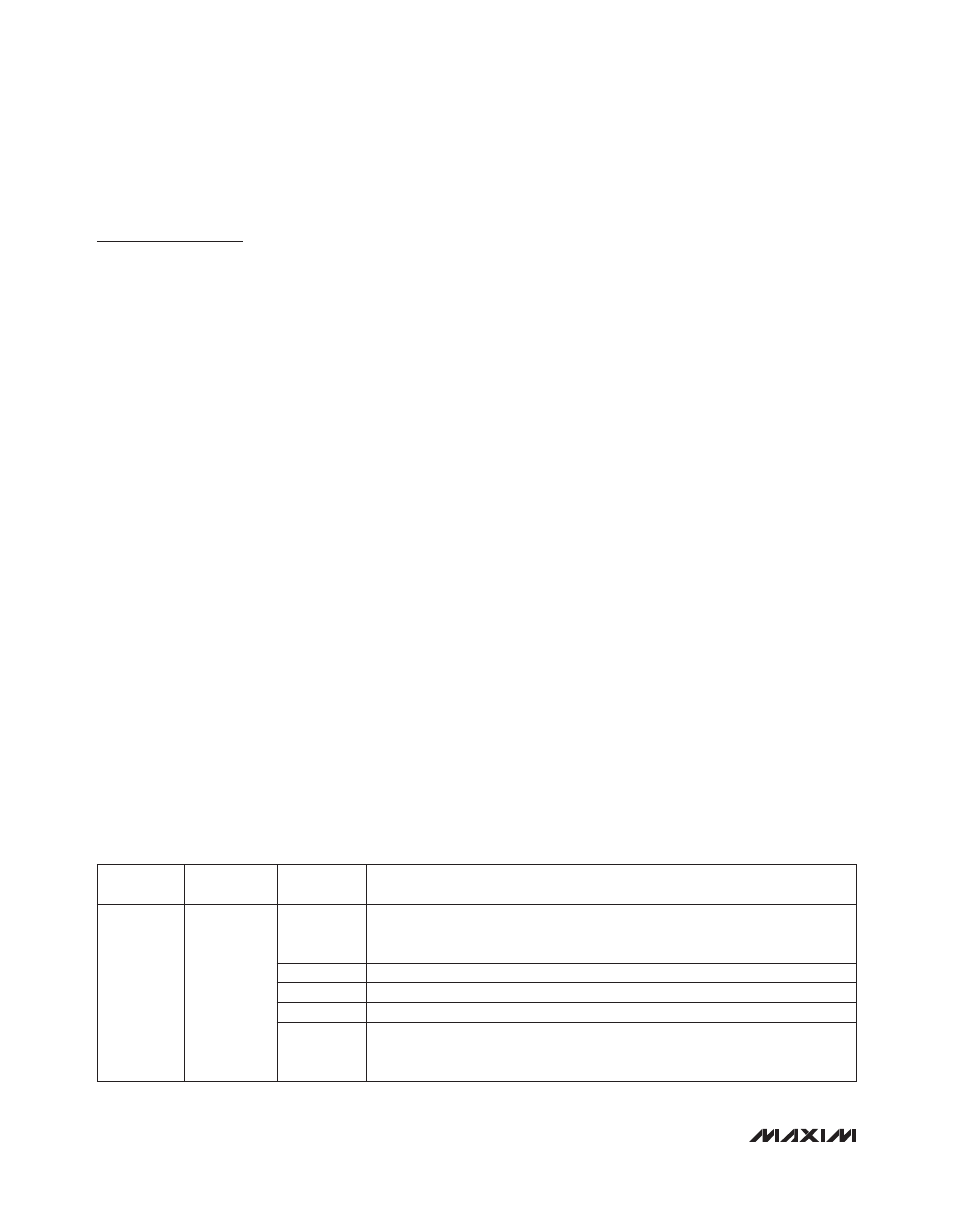

Table 1. Software Enable Configurations

REGISTER

ADDRESS

FLASH

ADDRESS

BIT RANGE

DESCRIPTION

73h

273h

[0]

Software Enable

1 = Sequencing enabled

0 = Power-down

[1]

Reserved

[2]

1 = Margin mode enabled

[3]

Reserved

[4]

Independent watchdog mode enable

1 = Watchdog timer is independent of EN input

0 = Watchdog timer boots after EN goes high and the boot-up delay completes