Rainbow Electronics MAX7030 User Manual

Page 13

MAX7030

Low-Cost, 315MHz, 345MHz, and 433.92MHz

ASK Transceiver with Fractional-N PLL

______________________________________________________________________________________

13

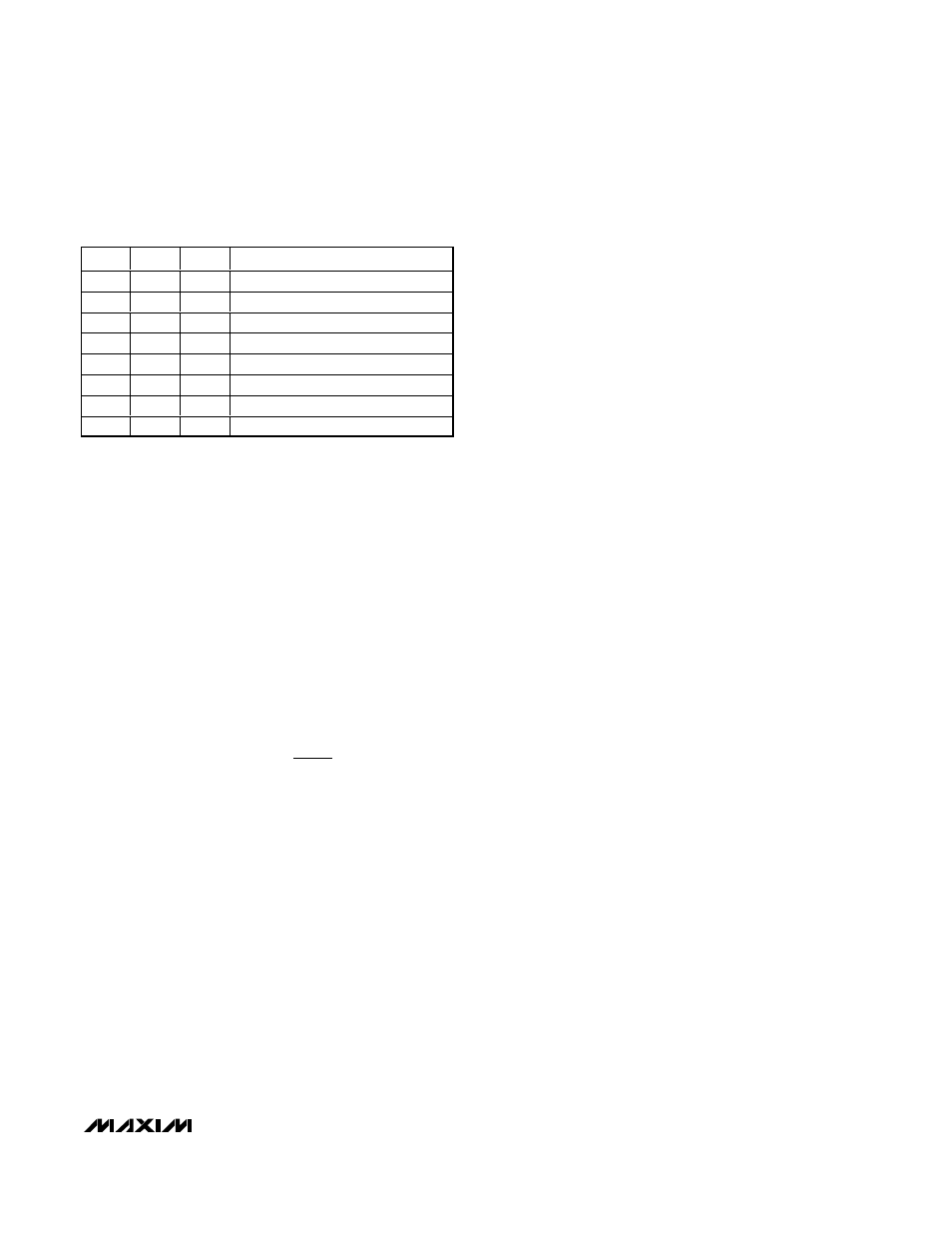

AGC Dwell-Time Settings

The AGC dwell timer holds the AGC in low-gain state

for a set amount of time after the power level drops

below the AGC switching threshold. After that set

amount of time, if the power level is still below the AGC

threshold, the LNA goes into high-gain state. This is

important for ASK since the modulated data may have

a high level above the threshold and low level below

the threshold, which without the dwell timer would

cause the AGC to switch on every bit.

The MAX7030 uses the three AGC control pins (AGC0,

AGC1, AGC2) to set seven user-controlled, dwell-timer

settings. The AGC dwell time is dependent on the crys-

tal frequency and the bit settings of the AGC control

pins. To calculate the dwell time, use the following

equation:

where K is an odd integer in decimal from 11 to 23, deter-

mined by the control pin settings shown in

Table

1.

To calculate the value of K, use the following equation

and use the next integer higher than the calculated

result:

K

≥ 3.3 x log

10

(Dwell Time x f

XTAL

)

For Manchester Code (50% duty cycle), set the dwell

time to at least twice the bit period. For nonreturn-to-

zero (NRZ) data, set the dwell to greater than the peri-

od of the longest string of zeros or ones. For example,

using Manchester Code at 315MHz (f

XTAL

=

12.679MHz) with a data rate of 2kbps (bit period =

250µs), the dwell time needs to be greater than 500µs:

K

≥ 3.3 x log

10

(500µs x 12.679)

≈ 12.546

Choose the AGC pin settings for K to be the next odd-

integer value higher than 12.546, which is 13. This says

that AGC1 is set high and AGC0 and AGC2 are set low.

Mixer

A unique feature of the MAX7030 is the integrated

image rejection of the mixer. This eliminates the need

for a costly front-end SAW filter for many applications.

The advantage of not using a SAW filter is increased

sensitivity, simplified antenna matching, less board

space, and lower cost.

The mixer cell is a pair of double-balanced mixers that

perform an IQ downconversion of the RF input to the

10.7MHz intermediate frequency (IF) with low-side

injection (i.e., f

LO

= f

RF

- f

IF

). The image-rejection circuit

then combines these signals to achieve a typical 46dB

of image rejection over the full temperature range. Low-

side injection is required as high-side injection is not

possible due to the on-chip image rejection. The IF out-

put is driven by a source follower, biased to create a

driving impedance of 330

Ω to interface with an off-chip

330

Ω ceramic IF filter. The voltage-conversion gain dri-

ving a 330

Ω load is approximately 20dB. Note that the

MIXIN+ and MIXIN- inputs are functionally identical.

Integer-N Phase-Locked Loop (PLL)

The MAX7030 utilizes a fixed-integer-N PLL to generate

the receive LO. All PLL components, including the loop

filter, voltage-controlled oscillator, charge pump, asyn-

chronous 24x divider, and phase-frequency detector

are integrated internally. The loop bandwidth is approx-

imately 500kHz. The relationship between RF, IF, and

reference frequencies is given by:

f

REF

= (f

RF

- f

IF

) / 24

Dwell Time

f

K

XTAL

=

2

AGC2

AGC1

AGC0

DESCRIPTION

0

0

0

AGC disabled, high gain selected

0

0

1

K = 11

0

1

0

K = 13

0

1

1

K = 15

1

0

0

K = 17

1

0

1

K = 19

1

1

0

K = 21

1

1

1

K = 23

Table

1. AGC Dwell Time Settings for

MAX7030