Rainbow Electronics MAX7358 User Manual

Page 5

MAX7356/MAX7357/MAX7358

1-to-8 I

2

C Bus Switches/Multiplexers with Bus

Lock-Up Detection, Isolation, and Notification

_______________________________________________________________________________________

5

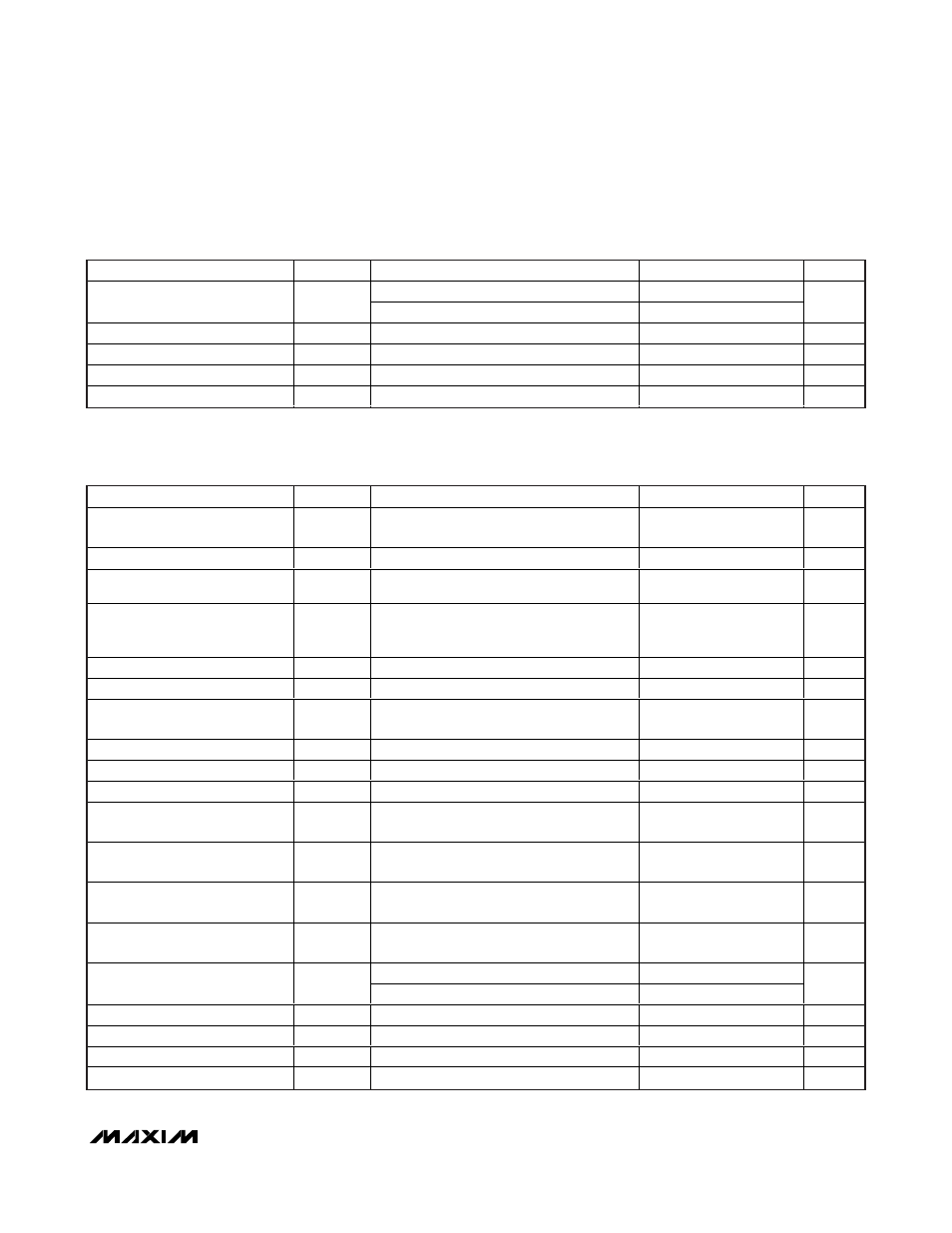

TIMING CHARACTERISTICS (STANDARD-MODE) (Figures 1, 2, 3) (continued)

(V

DD

= 2.3V to 5.5V, T

A

= -40°C to +85°C, unless otherwise noted.) (Notes 2, 6)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

(High to low)

1

Data Valid Time

t

VD;DAT

(Low to high)

0.6

µs

Data Valid Acknowledge

t

VD:ACK

1

µs

Low-Level Reset Time

t

WL(rst)

5

ns

Reset Time

t

rst

500

ns

Recovery to Start

t

REC;STA

0

ns

TIMING CHARACTERISTICS (FAST-MODE) (Figures 1, 2, 3)

(V

DD

= 2.3V to 5.5V, T

A

= -40°C to +85°C, unless otherwise noted.) (Notes 2, 6)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Propagation Delay from SDA to

SD_ or SCL to SC_

t

PD

(Note 7)

0.3

ns

SCL Clock Frequency

f

SCL

0

400

kHz

Bus Free Time Between a STOP

and START Condition

t

BUF

1.3

µs

Hold Time (Repeated) START

Condition After this Period,

the Fi r st C l ock P ul se i s Gener ated

t

HD;STA

0.6

µs

LOW Period of the SCL Clock

t

LOW

1.3

µs

HIGH Period of the SCL Clock

t

HIGH

0.6

µs

Setup Time for a Repeated

START Condition

t

SU;STA

0.6

µs

Setup Time for a STOP Condition

t

SU;STO

0.6

µs

Data Hold Time

t

HD;DAT

(Note 8)

0

0.9

µs

Data Setup Time

t

SU;DAT

100

ns

Rise Time of Both SDA and SCL

Signals

t

R

20 +

0.1C

b

300

ns

Fall Time of Both SDA and SCL

Signals

t

F

20 +

0.1C

b

300

ns

Capacitive Load for Each Bus

Line

C

b

400

pF

Pulse Width of Spikes that Must

be Suppressed by the Input Filter

t

SP

50

ns

(High to low)

1

Data Valid Time

t

VD;DAT

(Low to high)

0.6

µs

Data Valid Acknowledge

t

VD;ACK

1

µs

Low-Level Reset Time

t

WL(rst)

5

ns

Reset Time

t

rst

500

ns

Recovery to START

t

REC;STA

0

ns