Rainbow Electronics MAX7358 User Manual

Page 11

MAX7356/MAX7357/MAX7358

1-to-8 I

2

C Bus Switches/Multiplexers with Bus

Lock-Up Detection, Isolation, and Notification

______________________________________________________________________________________

11

Bus Lock-Up Detection, Isolation,

and Notification Operation

(MAX7357/MAX7358)

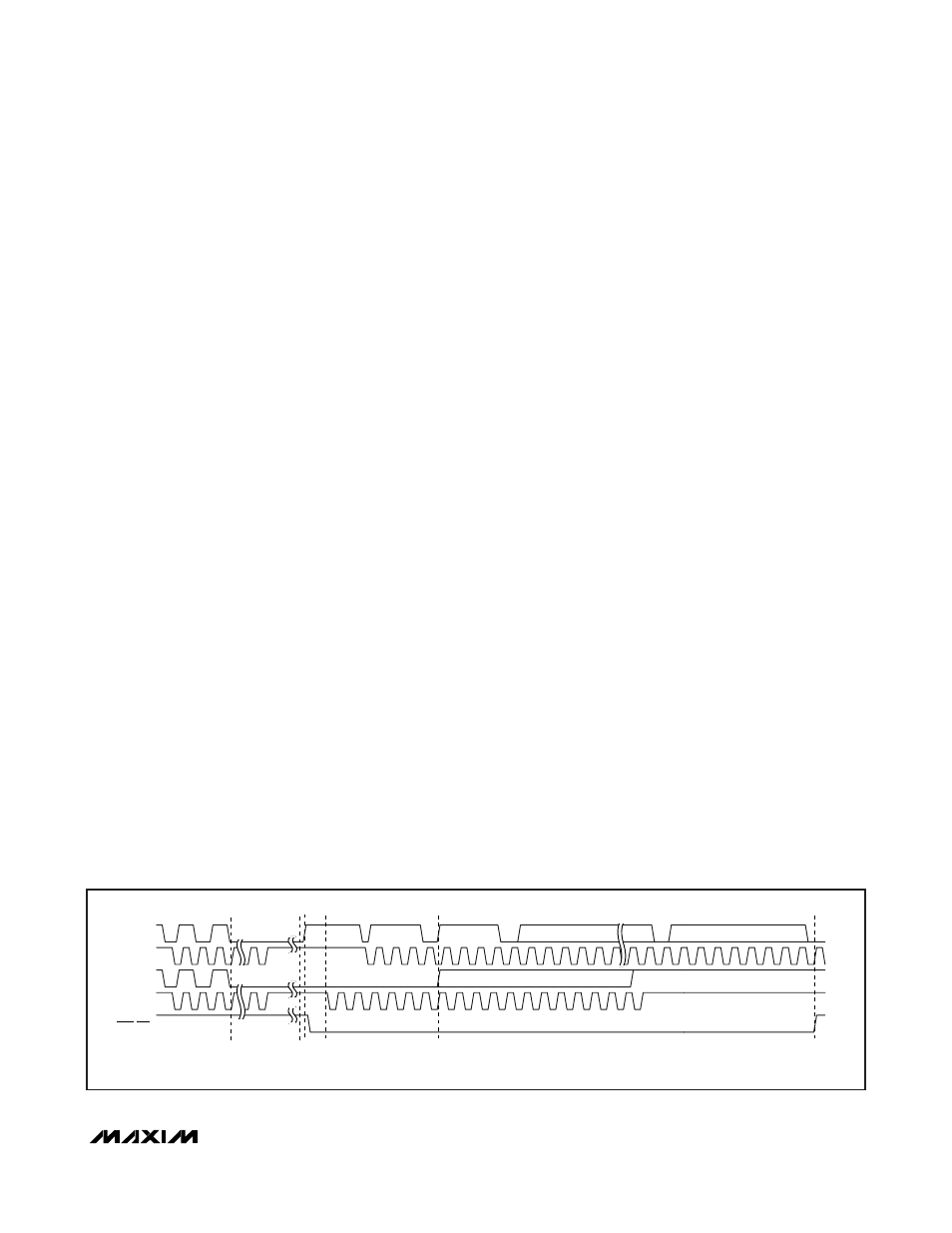

SDA Stuck Low

If either line of any downstream bus is low for a period

exceeding 25ms between t

1

and t

2

in Figure 6, the

MAX7357/MAX7358 detect a lock-up fault on that bus

and takes the action configured by the user. If the lock-

up is not on the main bus, SDA and SCL return to the

high state at the same time. The MAX7357 or MAX7358

then identifies which SD_ or SC_ is still pulled low. If the

optional interrupt function is enabled (by setting B0 of

the configuration register), an active-low interrupt is

generated at RST/INT.

If B4 in the configuration register is set to 1, then only

faults on connected buses cause the MAX7357 or

MAX7358 to disconnect all buses from each other.

When this is the case, faults detected on disconnected

buses set the flag in the lock-up status register, and, if

enabled, notify the host of the fault, but do not discon-

nect the buses from one another.

B1 of the configuration register enables the flush-out

sequence. If this bit is set to 1, the MAX7357 or

MAX7358 attempts to send a flush-out sequence over

the locked SD_ and SC_ pair (the sequence begins at

t

5

in Figure 6). If the flush-out sequence is successful,

the locked bus (SD_ and SC_) is released at t

6

(Figure

6). The I

2

C master (at SDA and SCL) reads the

MAX7357 or MAX7358 lock-up status register to iden-

tify the locked-up bus. If RST/INT is enabled as an

interrupt, it is released once a read command to the

lock-up indication register is received by the MAX7357

or MAX7358 (shown at t

7

in Figure 6). The RST/INT

can also be automatically released after a 1.6s delay

by setting bit 2 of the configuration register.

Preconnection Wiggle Test

(Stuck High Fault)

(MAX7357/MAX7358)

By setting bit B7 in the configuration register to 1, a pre-

connection wiggle test is enabled for all downstream

buses. This test only runs on the downstream bus when

the bus is selected through the switch control register.

Enabling this test does not affect any bus that is already

connected to the host bus; however, deselecting and

subsequently reselecting the bus will cause the test to

occur. The test is performed when the switch control reg-

ister bit (or bits if multiple buses are selected in the same

I

2

C transaction) toggles from 0 to 1 and a stop condition

is received. It consists of the MAX7357 or MAX7358

pulling the downstream clock line low, then the down-

stream data line low. Both lines are checked for a nomi-

nal low value, and then the clock line is released followed

by the data line (Note: This is an I

2

C stop condition and

is seen by any I

2

C devices connected to the extended

bus). If either the clock or data line (or both) fail to pull

low during the test, the MAX7357 or MAX7358 do not

allow that downstream bus to connect to the host. If the

optional interrupt notification bit is set (B0), the device

notifies the host that a fault has occurred. The I

2

C master

can then read the MAX7357 or MAX7358 registers to find

out which bus or buses caused the fault. Faults detected

by this test are stored in the preconnection fault register

(0x06). The stuck high Fault register is cleared once this

register is read, resetting the device, or disabling the

preconnection test.

Device Address

The MAX7356/MAX7357/MAX7358 family of devices

has selectable device addresses through three external

inputs. The slave address consists of 4 fixed bits

(A6–A3 set to 1110); followed by 3 pin-programmable

bits (A2, A1, A0), as shown in Figure 7. The addresses

A2, A1, and A0 can also be driven dynamically if

required, but the values must be stable when they are

expected in the address sequence.

RST/INT

BYTE1

FLUSH-OUT DATA

NOTE: THE FLUSH-OUT SEQUENCE RUNS AT AN SC_ FREQUENCY OF 40kHz.

THE HOST MAY COMMUNICATE AT UP TO 400kHz. THE TIMING SHOWN IS NOT TO SCALE.

BYTE4

t

1

t

2

t

3

t

4

t

5

t

6

t

7

SDA

SCL

SD_

SC_

Figure 6. Bus Lock-Up Detection, Isolation, and Notification Timing Diagram