Texas Instruments MSP430x11x1 User Manual

Page 31

MSP430x11x1

MIXED SIGNAL MICROCONTROLLER

SLAS241C – SEPTEMBER 1999 – REVISED JUNE 2000

31

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

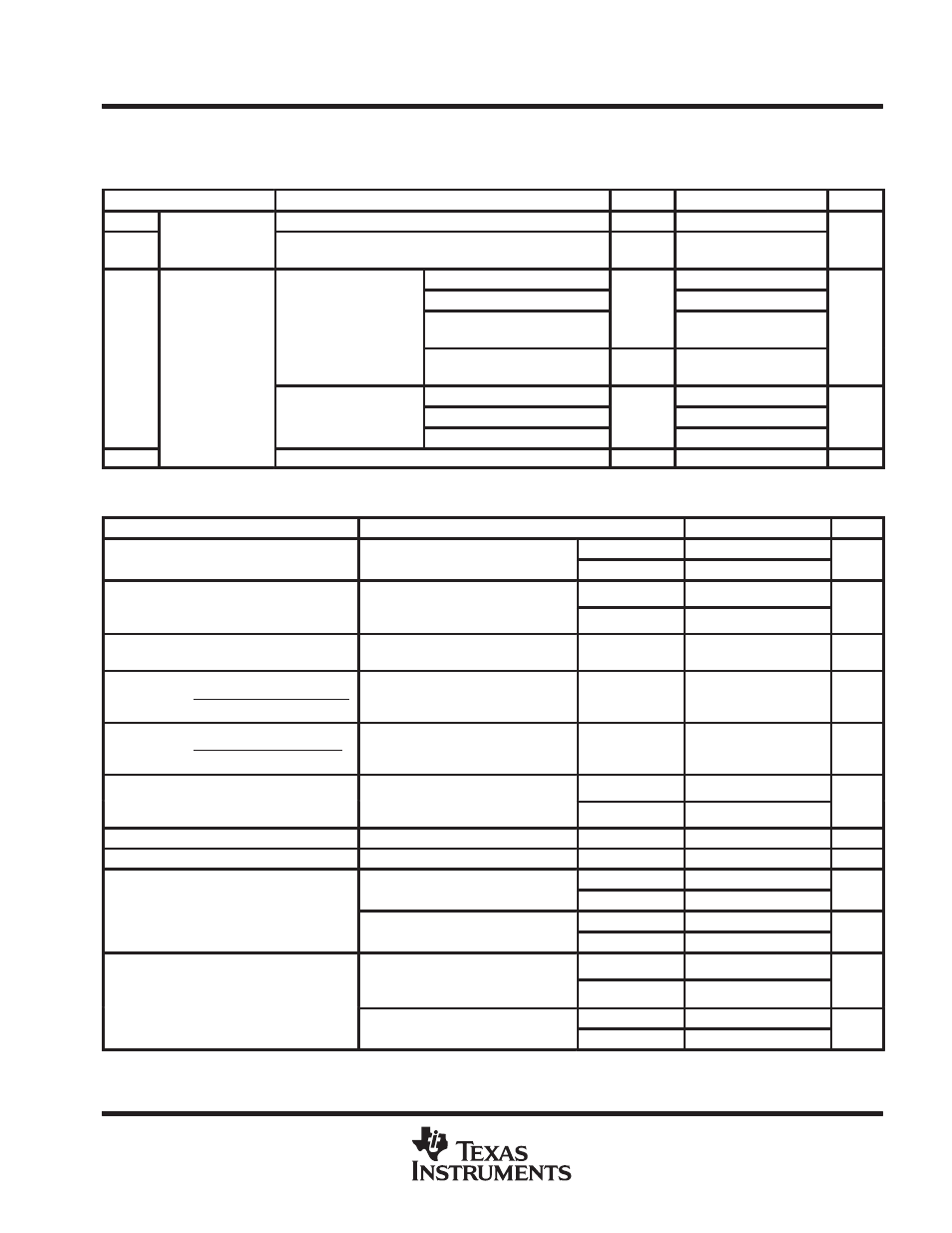

electrical characteristics over recommended ranges of supply voltage and operating free-air

temperature (unless otherwise noted) (continued)

outputs P1.x, P2.x, TAx

PARAMETER

TEST CONDITIONS

VCC

MIN

TYP

MAX

UNIT

f(P20)

P2.0/ACLK,

CL = 20 pF

2.2 V/3 V

fSystem

f(TAx)

Output frequency

TA0, TA1, TA2,

CL = 20 pF

Internal clock source, SMCLK signal applied (see Note 16)

2.2 V/3 V

dc

fSystem

MHz

fSMCLK = fLFXT1 = fXT1

40%

60%

P1 4/SMCLK

fSMCLK = fLFXT1 = fLF

2 2 V/3 V

35%

65%

P1.4/SMCLK,

CL = 20 pF

fSMCLK = fLFXT1/n

2.2 V/3 V

50%–

15 ns

50%

50%+

15 ns

t(Xdc)

Duty cycle of O/P

frequency

fSMCLK = fDCOCLK

2.2 V/3 V

50%–

15 ns

50%

50%+

15 ns

P2 0/ACLK

fP20 = fLFXT1 = fXT1

40%

60%

P2.0/ACLK,

CL = 20 pF

fP20 = fLFXT1 = fLF

2.2 V/3 V

30%

70%

CL = 20 F

fP20 = fLFXT1/n

50%

t(TAdc)

TA0, TA1, TA2,

CL = 20 pF, Duty cycle = 50%

2.2 V/3 V

0

±

50

ns

NOTE 16: The limits of the system clock MCLK has to be met. MCLK and SMCLK can have different frequencies.

Comparator_A (see Note 17)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

I(DD)

CAON=1

CARSEL=0

CAREF=0

VCC = 2.2 V

25

40

µ

A

I(DD)

CAON=1, CARSEL=0, CAREF=0

VCC = 3 V

45

60

µ

A

I(Refladder/

CAON=1, CARSEL=0,

CAREF=1/2/3

No load at

VCC = 2.2 V

30

50

µ

A

(Refladder/

RefDiode)

CAREF=1/2/3, No load at

P2.3/CA0/TA1 and P2.4/CA1/TA2

VCC = 3 V

45

71

µ

A

V(IC)

Common-mode input

voltage

CAON =1

VCC = 2.2 V/3 V

0

VCC–1

V

V(Ref025)

See Figure 5

Voltage @ 0.25 V

CC

node

V

CC

PCA0=1, CARSEL=1, CAREF=1,

No load at P2.3/CA0/TA1 and

P2.4/CA1/TA2, See Figure 5

VCC = 2.2 V/3 V

0.23

0.24

0.25

V(Ref050)

See Figure 5

Voltage @ 0.5 V

CC

node

V

CC

PCA0=1, CARSEL=1, CAREF=2,

No load at P2.3/CA0/TA1 and

P2.4/CA1/TA2, See Figure 5

VCC = 2.2 V/3 V

0.47

0.48

0.5

V(R fVT)

PCA0=1, CARSEL=1, CAREF=3,

No load at P2 3/CA0/TA1 and

VCC = 2.2 V

430

550

645

mV

V(RefVT)

No load at P2.3/CA0/TA1 and

P2.4/CA1/TA2

VCC = 3 V

450

565

660

mV

V(offset)

Offset voltage

See Note 18

VCC = 2.2 V/3 V

–30

30

mV

Vhys

Input hysteresis

CAON=1

VCC = 2.2 V/3 V

0

0.7

1.4

mV

TA = 25

°

C, Overdrive 10 mV, With-

VCC = 2.2 V

160

210

300

ns

t(

LH)

A

out filter: CAF=0

VCC = 3 V

90

150

200

ns

t(response LH)

TA = 25

°

C, Overdrive 10 mV, With

VCC = 2.2 V

1.6

1.9

3.4

µ

s

A

filter: CAF=1

VCC = 3 V

1.1

1.5

2.6

µ

s

TA = 25

°

C,

Overdrive 10 mV without filter:

VCC = 2.2 V

160

210

300

ns

t(response HL)

Overdrive 10 mV, without filter:

CAF=0

VCC = 3 V

90

150

200

ns

(res onse HL)

TA = 25

°

C,

VCC = 2.2 V

1.6

1.9

3.4

µ

s

A

Overdrive 10 mV, with filter: CAF=1

VCC = 3 V

1.1

1.5

2.6

µ

s

NOTES: 17. The leakage current for the Comparator_A terminals is identical to Ilkg(Px.x) specification.

18. The input offset voltage can be cancelled by using the CAEX bit to invert the Comparator_A inputs on successive measurements.

The two successive measurements are then summed together.