Figure 4-11. trig1 input signal timing, Figure 4-12. trig1 output signal timing, Trig2 signal – National Instruments NI PCI-6110 User Manual

Page 50: Trig2 signal -20

Chapter 4

Connecting Signals

4-20

ni.com

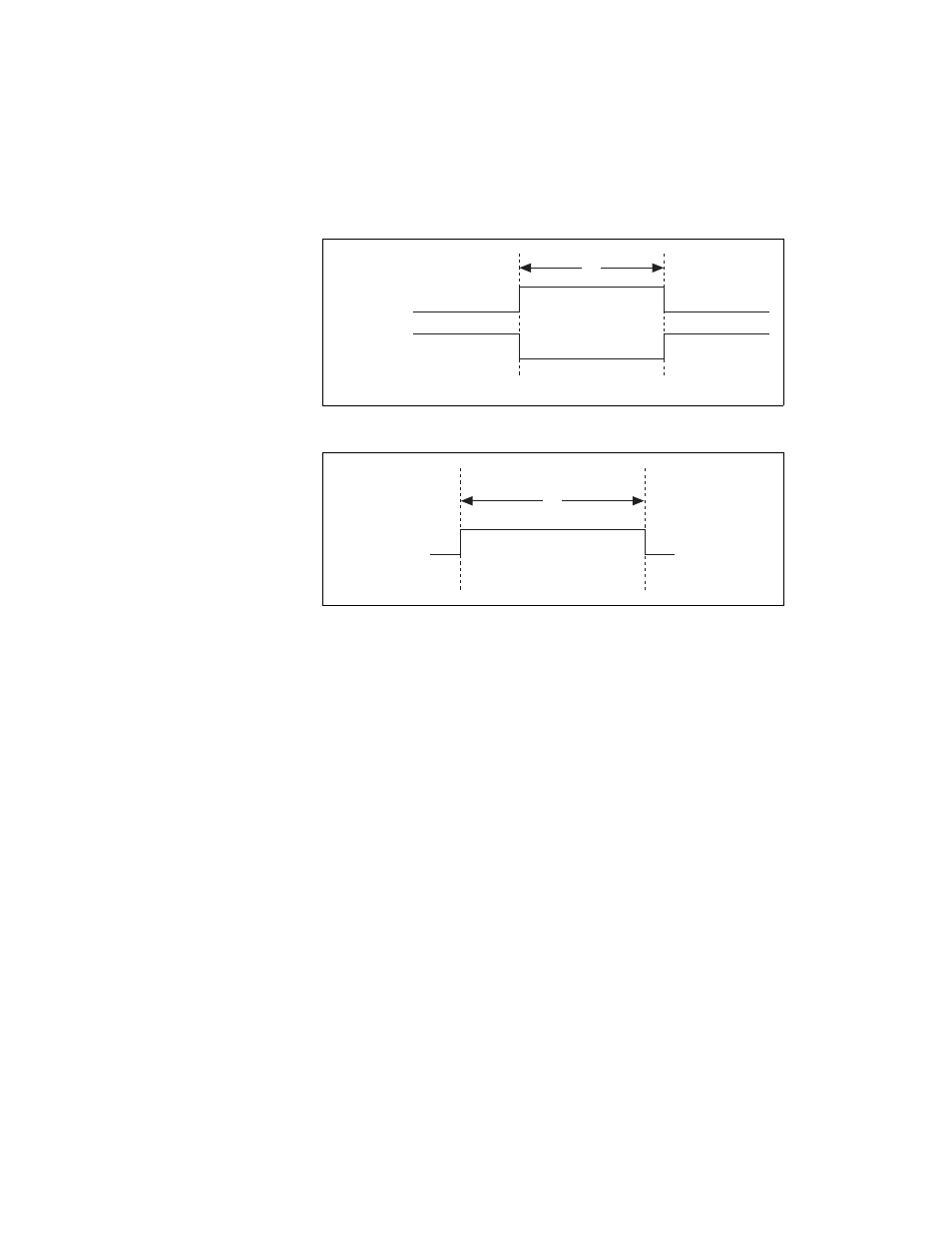

Figures 4-11 and 4-12 show the timing requirements for TRIG1.

Figure 4-11. TRIG1 Input Signal Timing

Figure 4-12. TRIG1 Output Signal Timing

The device also uses TRIG1 to initiate pretriggered DAQ operations. In

most pretriggered applications, TRIG1 is generated by a software trigger.

Refer to the TRIG2 signal description for a complete description of the use

of TRIG1 and TRIG2 in a pretriggered DAQ operation.

TRIG2 Signal

Any PFI pin can receive as an input the TRIG2 signal, which is available

as an output on the PFI1/TRIG2 pin. Refer to Figure 4-10 for the

relationship of TRIG2 to the DAQ sequence.

As an input, TRIG2 is configured in the edge-detection mode. You can

select any PFI pin as the source for TRIG2 and configure the polarity

selection for either rising or falling edge. The selected edge of TRIG2

initiates the posttriggered phase of a pretriggered DAQ sequence. In

pretriggered mode, the TRIG1 signal initiates the data acquisition. The scan

counter (SC) indicates the minimum number of scans before TRIG2 can be

recognized. After the SC decrements to zero, it is loaded with the number

of posttrigger scans to acquire while the acquisition continues. The device

ignores TRIG2 if it is asserted prior to the SC decrementing to zero. After

Rising-Edge

Polarity

Falling-Edge

Polarity

t

w

= 10 ns minimum

t

w

t

w

= 25 to 50 ns

t

w