Update* signal, Figure 4-24. update* input signal timing, Figure 4-25. update* output signal timing – National Instruments NI PCI-6110 User Manual

Page 59: Update* signal -29

Chapter 4

Connecting Signals

© National Instruments Corporation

4-29

UPDATE* Signal

Any PFI pin can externally input the UPDATE* signal, which is available

as an output on the PFI5/UPDATE* pin.

As an input, UPDATE* is configured in the edge-detection mode. You can

select any PFI pin as the source for UPDATE* and configure the polarity

selection for either rising or falling edge. The selected edge of UPDATE*

updates the outputs of the DACs. In order to use UPDATE*, you must set

the DACs to posted-update mode.

As an output, UPDATE* reflects the actual update pulse that is connected

to the DACs, even if the updates are being externally generated by another

PFI. The output is an active low pulse with a pulse width of 50 to 75 ns.

This output is set to high-impedance at startup.

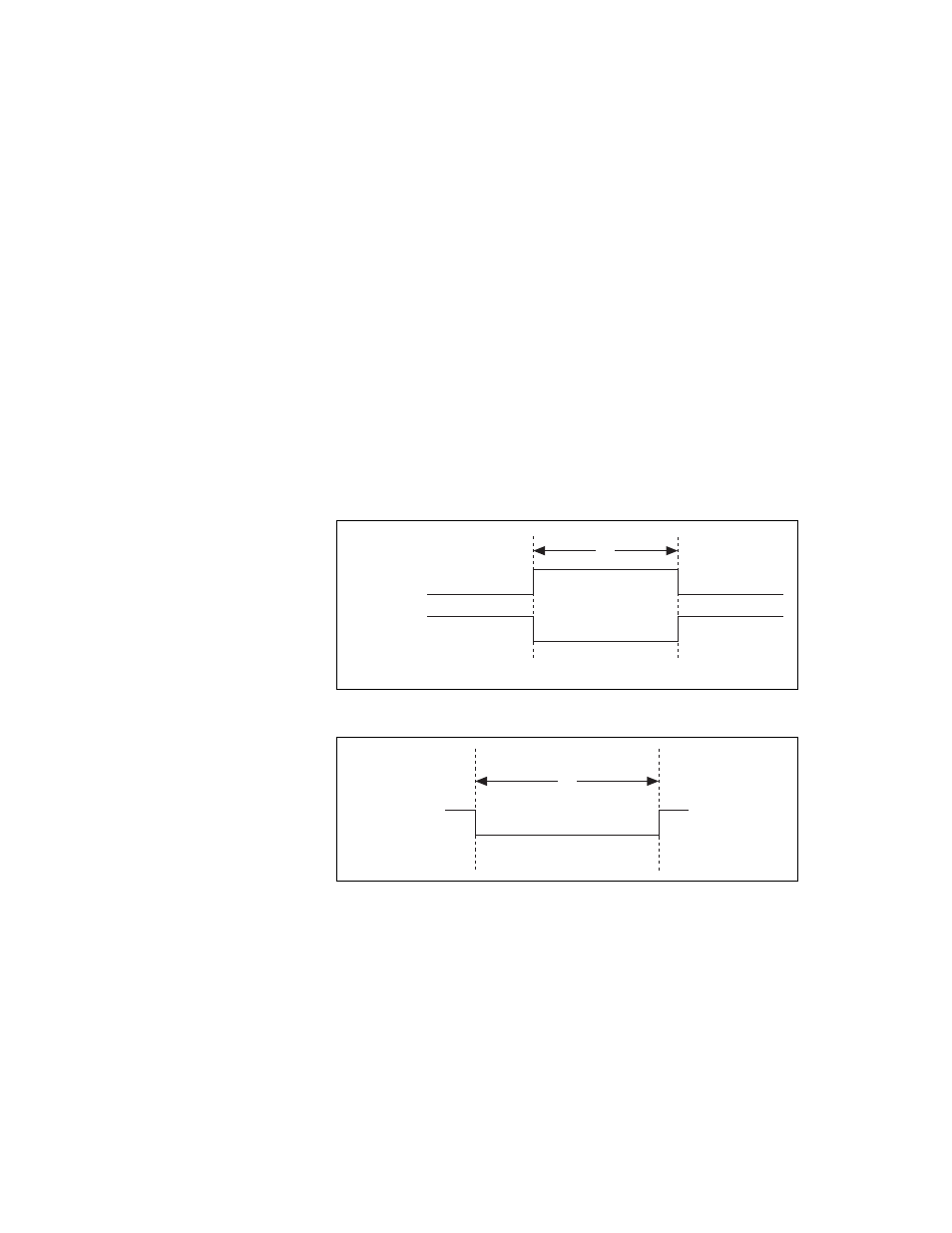

Figures 4-24 and 4-25

show the timing requirements for UPDATE*.

Figure 4-24. UPDATE* Input Signal Timing

Figure 4-25. UPDATE* Output Signal Timing

The DACs are updated within 100 ns of the leading edge. Separate the

UPDATE* pulses with enough time that new data can be written to the

DAC latches.

Rising-Edge

Polarity

Falling-Edge

Polarity

t

w

= 10 ns minimum

t

w

t

w

= 50 to 75 ns

t

w