Figure7.22 target asynchronous receive, Target asynchronous receive, Initiator and target synchronous transfers – LSI 53C810A User Manual

Page 212: Target asynchronous receive (5 mbytes/s)

7-30

Electrical Characteristics

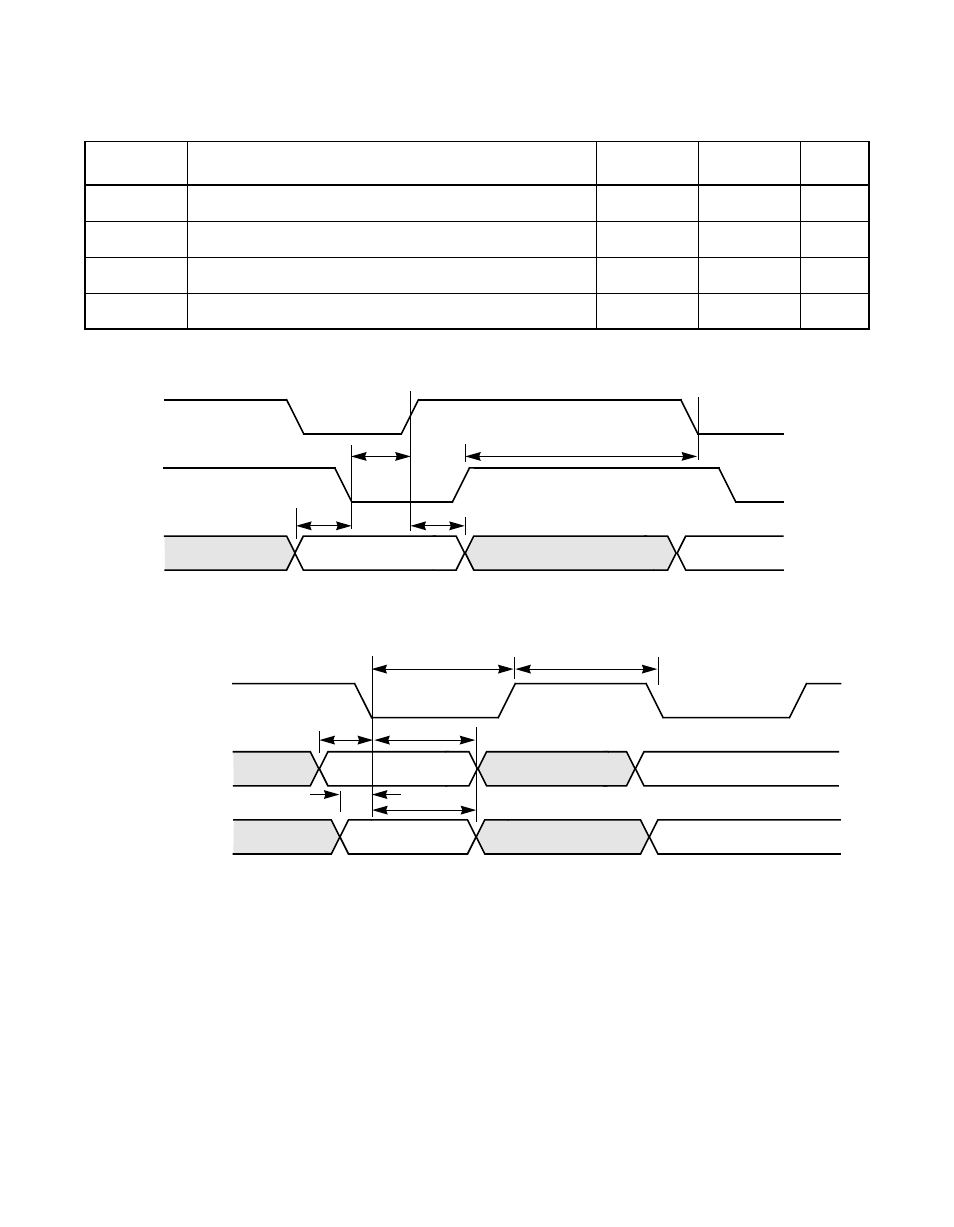

Figure 7.22 Target Asynchronous Receive

Figure 7.23 Initiator and Target Synchronous Transfers

Table 7.20

Target Asynchronous Receive (5 Mbytes/s)

Symbol

Parameter

Min

Max

Unit

t

1

SREQ/ deasserted from SACK/ asserted

10

–

ns

t

2

SREQ/ asserted from SACK/ deasserted

10

–

ns

t

3

Data setup to SREQ/ asserted

0

–

ns

t

4

Data hold from SACK/ asserted

0

–

ns

SREQ/

SACK/

SD[7:0],

SDP/

n

n + 1

t

2

t

1

t

3

t

4

Valid n

Valid n + 1

n + 1

n

SREQ/

or SACK/

Send Data

SD[7:0], SDP/

Receive Data

SD[15:0]/,

SDP[1:0]/

t

3

t

4

t

1

t

2

t

5

t

6

n

n + 1

Valid n

Valid n + 1

Valid n

Valid n + 1