27 eeprom operation/status register (eosr) – SBE HighWire HW400c/2 User Manual

Page 74

HighWire HW400c/2 User Reference Guide Rev 1.0

R)

king the programming

tatus after a write operation.

to write EEPROM word addresses 0x00-0x0F without the FAC jumper

stalled results in a write error, setting WERR bit. These addresses are reserved for

Ta

9

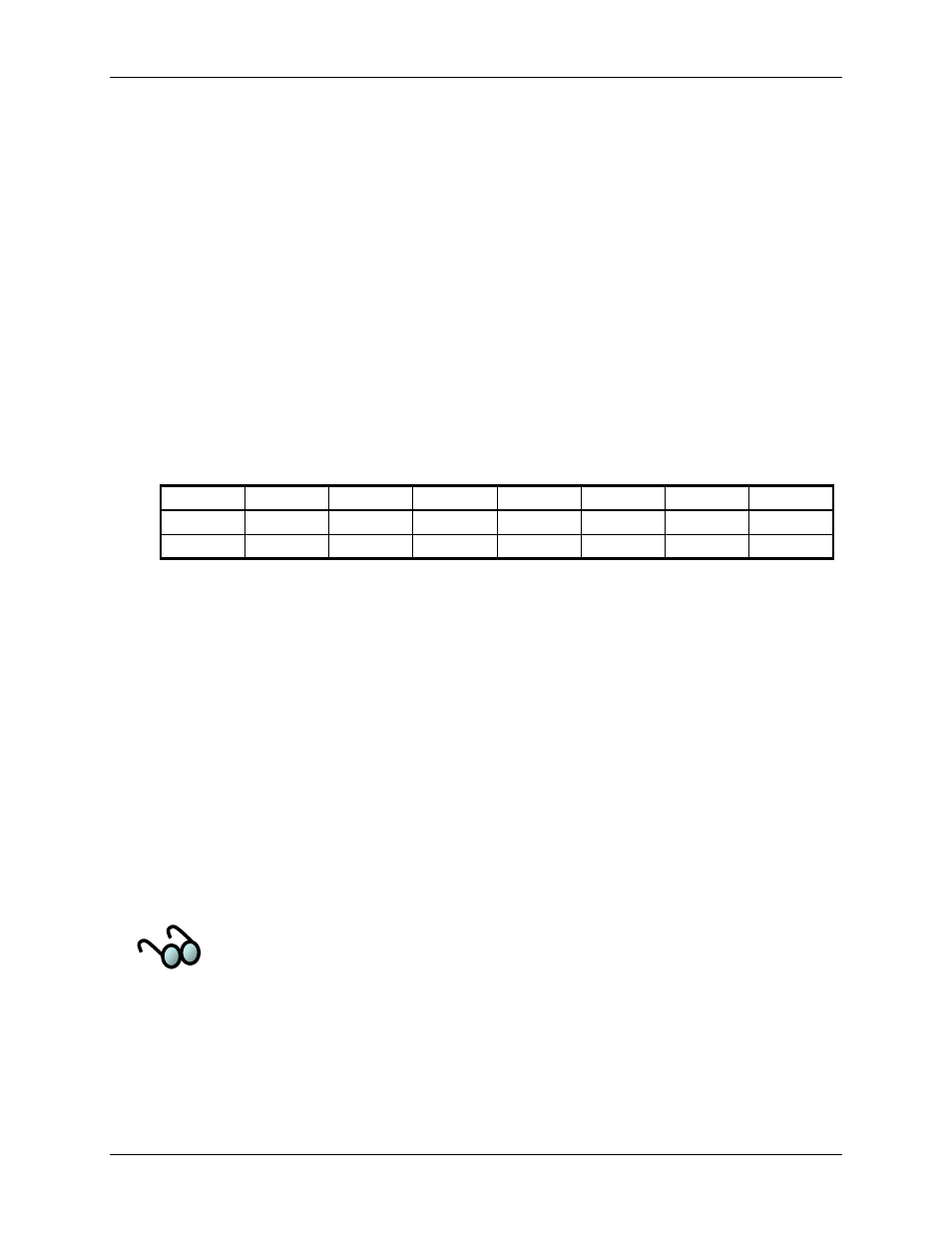

Bit 7

Bit 5

Bit 3

Bit 2

1

Bit 0

4.2.27 EEPROM Operation/Status Register (EOS

The EEPROM Operation and Status Register is a Read/Write register. It is used for

initiating a read or write operation to the EEPROM, and chec

s

Bits 0-3 are self-clearing, and bit 7 clears when the next operation is started.

Attempting

in

SBE board ID identification and are programmed by SBE during board

manufacturing.

ble 57. EEPROM Operation/Status Register (EOSR) Offset Address 0x2

Bit 6

Bit 4

Bit

WERR

d

Reserved

ERD EWDS

R EWEN

Reserve

EBSY

EW

R R R R W W W

W

EWEN:

Writing a “1” to this bit initiates a EWEN cycle, required before a write.

EWR:

Writing a “1” to this bit initiates a write, using the EAR address and

RD:

Writing a “1” to this bit initiates a read, using the EAR address and

EBSY

= 0

EEPROM is ready for next write operation

WE

0

Write operation completed successfully

For m

nsult the device data sheets. Devices supported include

EDR data.

EWDS:

Writing a “1” to this bit initiates a EWDS cycle, required after a write.

E

EDR data.

= 1

EEPROM is busy writing (no reads or writes allowed)

RR

=

= 1

Write error, operation not completed

ore information on the serial EEPROM, co

Atmel AT93C66A, Microchip 93LC66C, and ST Microelectronics M93C66.

October 10, 2006

Copyright 2006, SBE, Inc.

Page

62