6 ptmc reset register (prr), 7 ptmc control register (pcr) – SBE HighWire HW400c/2 User Manual

Page 63

HighWire HW400c/2 User Reference Guide Rev 1.0

4.2.6 PTMC Reset Register (PRR)

PTMC Reset Register (PRR) is a Read/Write register that asserts and de-asserts reset

to the individual PTMC sites. The Reset pulse applied to the PTMC modules must

conform to the PCI

standard, that is, it must be at least 10 PCI clock cycles long.

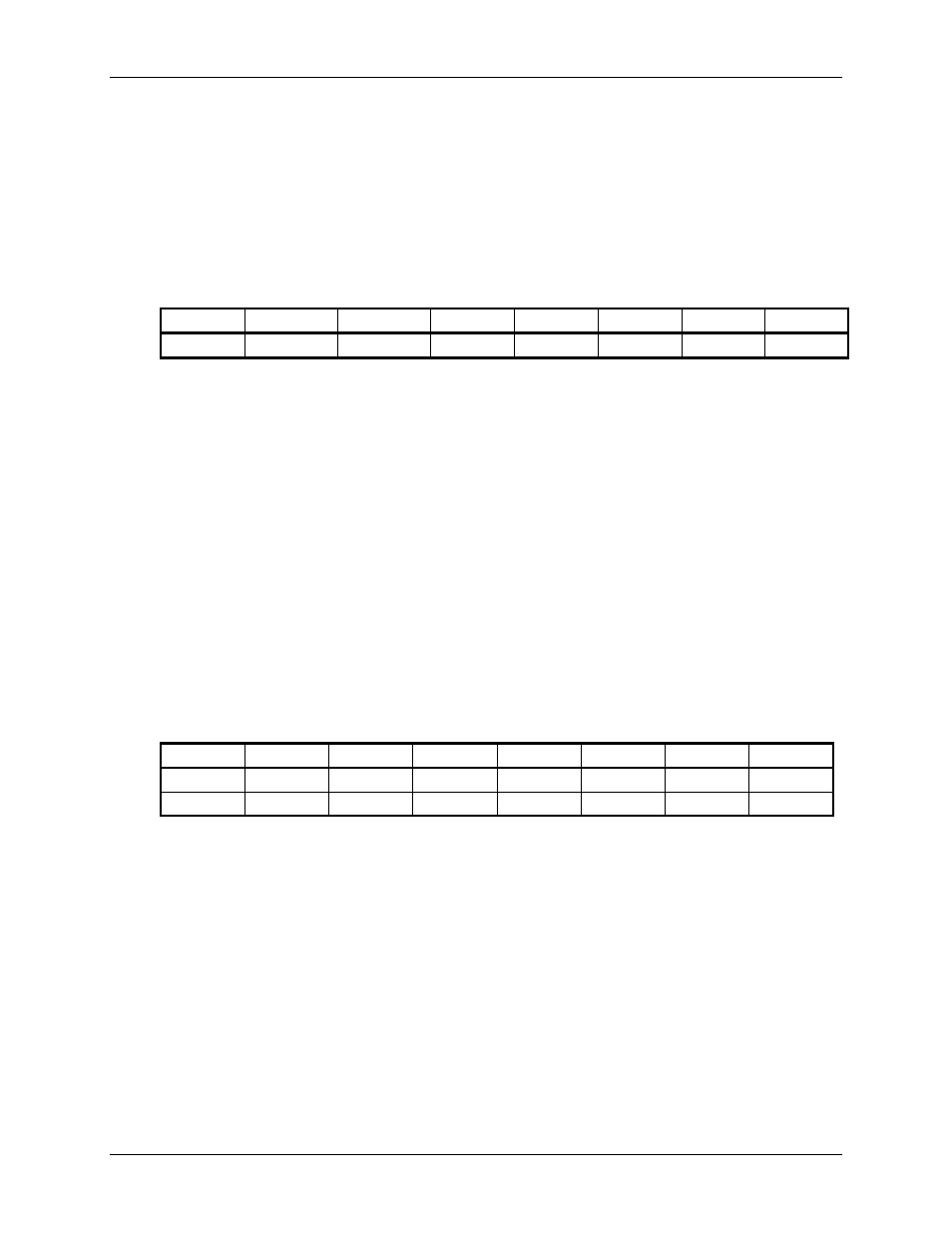

Table 35. PTMC Reset Register (PRR) Offset Address 0x09

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Re

d PMCRSTB PMCRSTA Re

d Re

d Re

d Re

d Re

d

serve

serve

serve

serve

serve

serve

P

= 0

De-a

S

T (de

lt state)

= 1 Assert PMC Site B RESET

De-

fault state)

Ass

4.2.7 PTMC Con

he PTMC Control Register (PCR) is a Read/Write register. The interoperability of

ach PTMC mezzanine card can be detected by reading this register. After reading

each card’s PTID bits, the processor can enable the card by setting the site’s PTEN

vention is required for PTIDx[2:0] = 010 or 101, which

are the codes for PT2MC and PT5MC, respectively. When either of these codes is

e

Control Register (PCR) Offset Address 0x0A

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

MCRSTB

ssert PMC ite B RESE

fau

PMCRSTA

= 0

assert PMC Site A RESET (de

= 1

ert PMC Site A RESET

trol Register (PCR)

T

e

bit to “1”. No processor inter

detected by the CPLD, the PTEN bit for the site is set to “1” automatically, and th

card in that site is enabled.

Table 36. PTMC

PTENB

PTIDA0

PTIDB2 PTIDB1 PTIDB0 PTENA PTIDA2 PTIDA1

R/W

R R R

R/W

R R R

P

ite

TIDB[2:0]

= 000

Site B is 32-bit PMC type, or is not present

ype, or PT7MC type

TENA

C Site A Enabled

TIDB[2:0]

= 000

Site A is 32-bit PMC type, or is not present

= 010

Site A is PT2MC type

= 101

Site A is PT5MC type

= 111

Site A is 64-bit PMC type, or PT7MC type

TENB

= 0

PTMC Site B Disabled

PTMC S

= 1

B Enabled

P

= 010

Site B is PT2MC type

= 101

Site B is PT5MC type

= 111

Site B is 64-bit PMC t

P

= 0

PTMC Site A Disabled

= 1

PTM

P

October 10, 2006

Copyright 2006, SBE, Inc.

Page

51