21 spi read byte offset register (sor), 22 read byte count register (rbc) – SBE HighWire HW400c/2 User Manual

Page 71

HighWire HW400c/2 User Reference Guide Rev 1.0

4.2.21 SPI Read Byte Offset Register (SOR)

g

ding from

e BCM5388 Ethernet Switch SPI port. In the case where the entire register is not

Tab

x1C

The SPI Byte Offset Select Register is a Read/Write register. It is used for selectin

the desired byte offset (within the register selected by the SAR) when rea

th

being read, the SOR can be set to a non-zero value to index to the desired starting

byte.

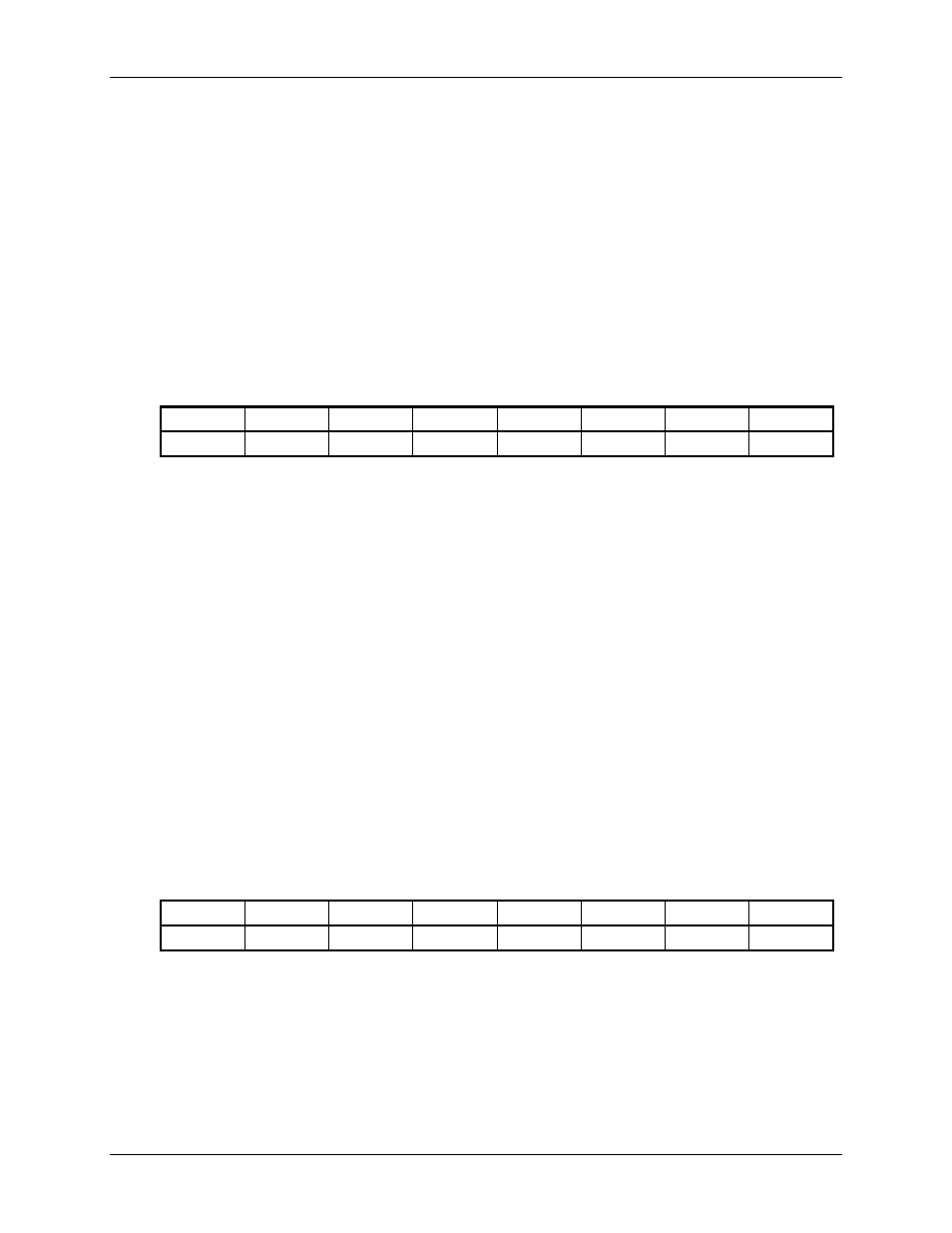

le 51. SPI Read Byte Offset Select Register (SOR) Offset Address 0

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Reserved Reserved Reserved Reserved Reserved

SOR2

SOR1

SOR0

SOR[2:0]

= 000

No by

= 001

Select 2 byte

= 010

Select 3

rd

byte

….

….

th

byte

4.2.22 Read Byt

Bit 7

Bit 5

Bit 3

Bit 2

1

Bit 0

te offset (Select 1

st

byte)

nd

= 111

Select 8

e Count Register (RBC)

The Read Byte Count Register is a Read/Write register. It is used for setting the

umber of bytes to be read when reading from the BCM5388 SPI port. When this

n

register is written, the internal SPI Read State Machine is initiated. After all

requested bytes are read from the BCM5388, the RBC value is cleared.

Table 52. Read Byte Count Register (RBC) Offset Address 0x1D

Bit 6

Bit 4

Bit

Reserved Re

ed Reserved Re

d

RBC3 RBC2 RBC1 RBC0

serv

serve

0]

= 0x1 – 0x8

ead from one to ei

5388

RBC[3:

R

ght bytes from the BCM

October 10, 2006

Copyright 2006, SBE, Inc.

Page

59