14 pll configuration register b (pllb) – SBE HighWire HW400c/2 User Manual

Page 67

HighWire HW400c/2 User Reference Guide Rev 1.0

4.2.14 PLL Configuration Register B (PLLB)

ter

long with PLLA) can help software determine the CPU operating frequency, as

well a

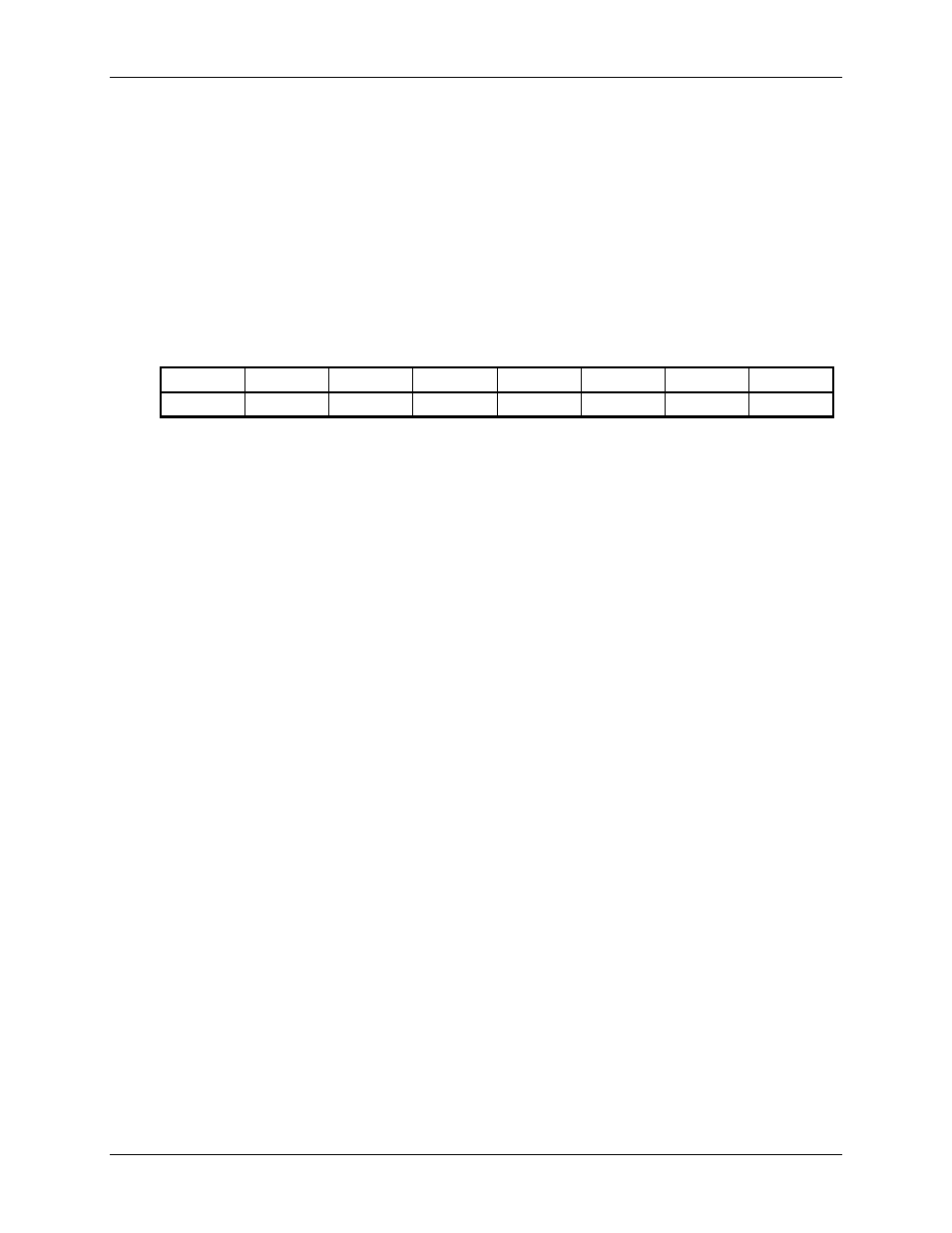

Table 43. PLL Configuration Register B (PLLB)

Addr

3

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

The PLL Configuration Register B (PLLB) is a Read-Only register. It contains the

settings for the System bus and Device bus (external) PLLs. Reading this regis

(a

s the Device bus operating frequency.

Offset

ess 0x1

Reserved

SPLL1

ed Reserved

DPLL1 DPLL0

Reserved

SPLL2 Reserv

SPLL[1:0] =

00

is 100 MHz

is 133 MHz

c/2

PLL[1:0]

400c/2

System

bus clock

= 01

System bus clock

= 10

System bus clock is 166 MHz (Default for HW400

standard version)

= 11

System bus clock is 200 MHz

D

= 00

= 01

Device bus clock is 100 MHz

Device bus clock is 133 MHz (Default for HW

standard version)

Reserved

Reserved

=

10

=

11

October 10, 2006

Copyright 2006, SBE, Inc.

Page

55