Figure 6.3 100m mii transmit timing diagram, Table 6.3 100m mii transmit timing values, Clock out - tx_clk data in - txd[3:0] t – SMSC FlexPWR LAN8710i User Manual

Page 57: Tx_en tx_er valid data

MII/RMII 10/100 Ethernet Transceiver with HP Auto-MDIX and flexPWR

®

Technology in a Small Footprint

Datasheet

SMSC LAN8710/LAN8710i

57

Revision 1.0 (04-15-09)

DATASHEET

6.2.1.2

100M MII Transmit Timing

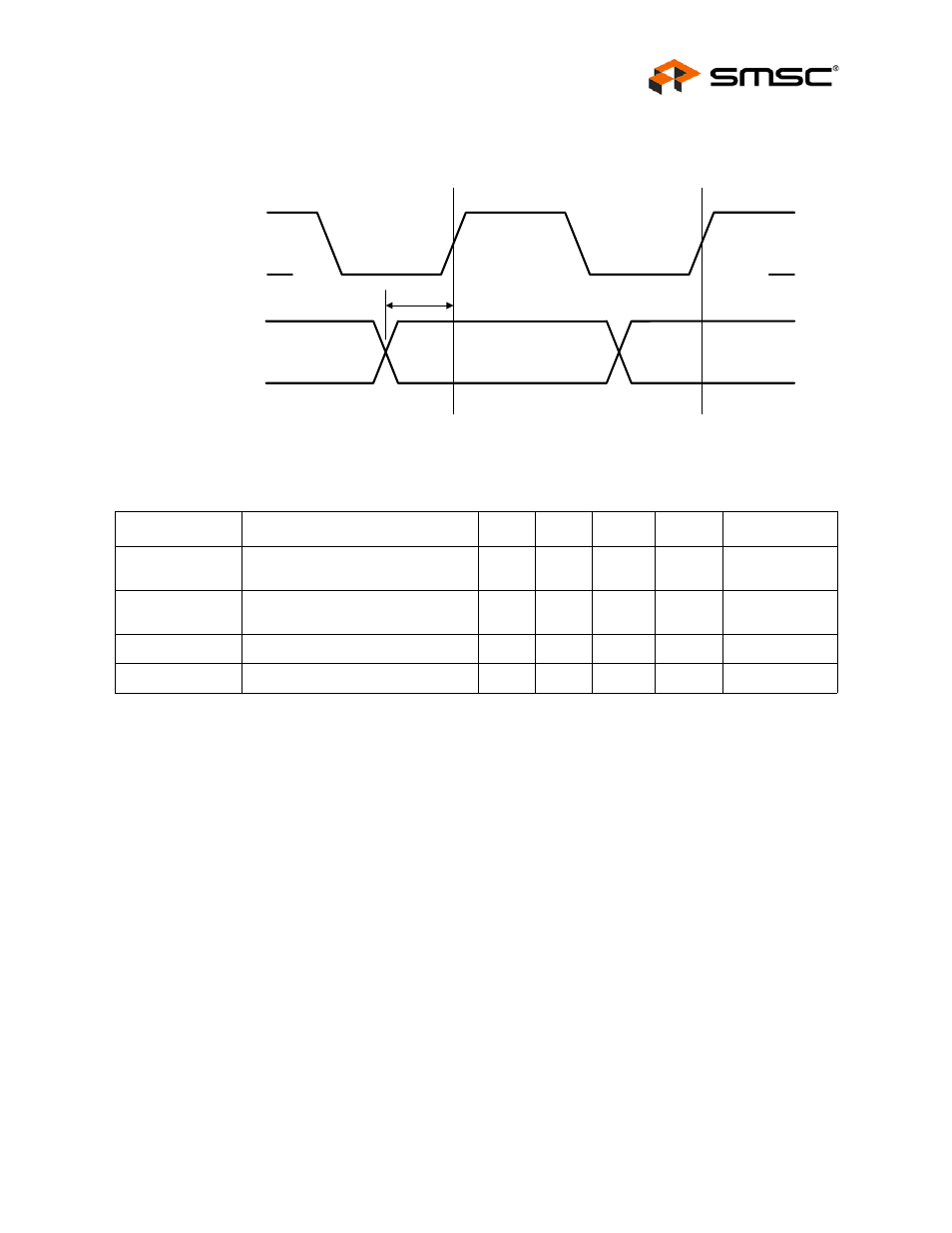

Figure 6.3 100M MII Transmit Timing Diagram

Table 6.3 100M MII Transmit Timing Values

PARAMETER

DESCRIPTION

MIN

TYP

MAX

UNITS

NOTES

T3.1

Transmit signals required setup to

TXCLK rising

12

ns

Transmit signals required hold

after TXCLK rising

0

ns

TXCLK frequency

25

MHz

TXCLK Duty-Cycle

50

%

Clock Out -

TX_CLK

Data In -

TXD[3:0]

T

3.1

TX_EN

TX_ER

Valid Data

This manual is related to the following products: