Figure 1.2 lan8710/lan8710i architectural overview, Datasheet – SMSC FlexPWR LAN8710i User Manual

Page 11

MII/RMII 10/100 Ethernet Transceiver with HP Auto-MDIX and flexPWR

®

Technology in a Small Footprint

Datasheet

SMSC LAN8710/LAN8710i

11

Revision 1.0 (04-15-09)

DATASHEET

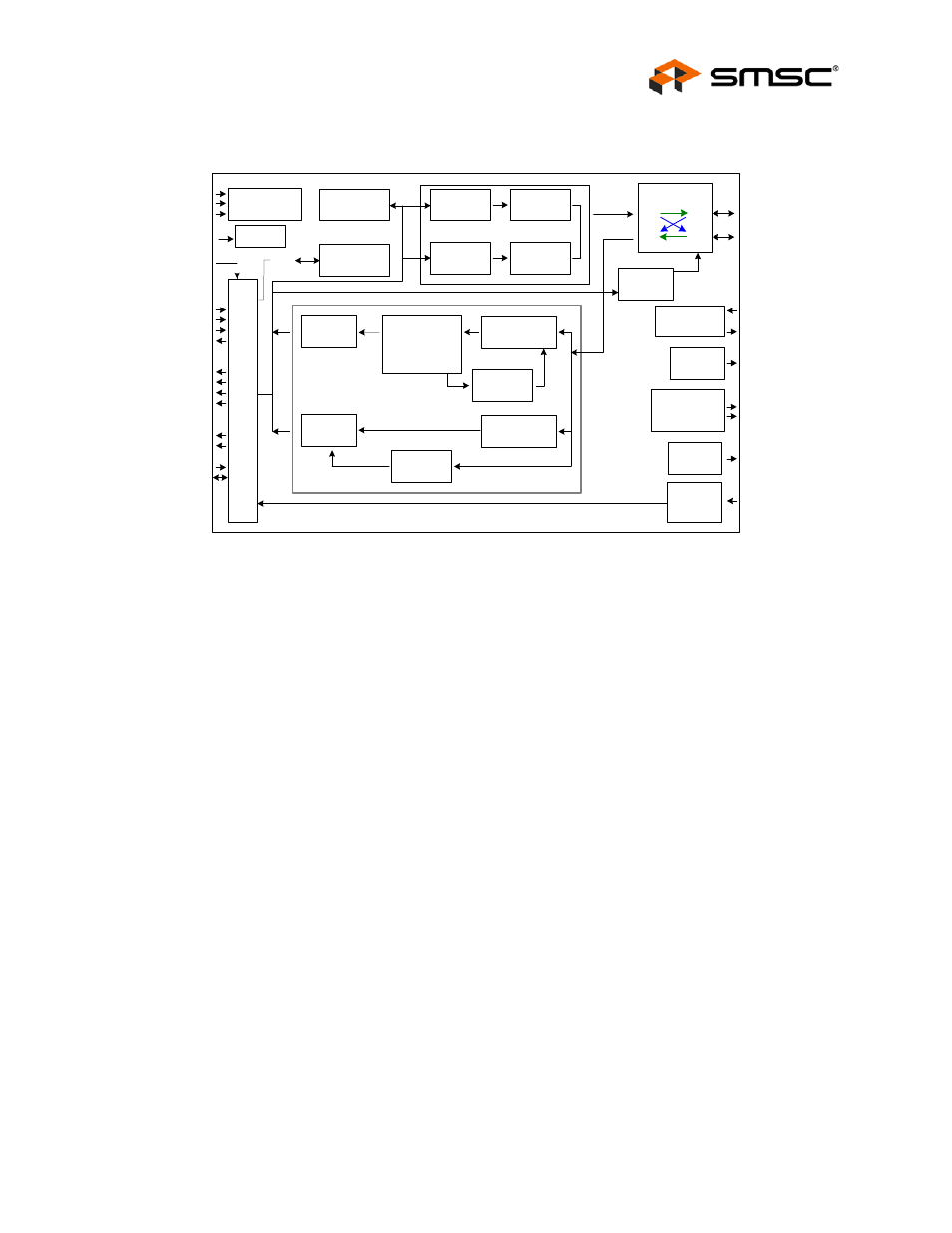

Figure 1.2 LAN8710/LAN8710i Architectural Overview

10M Rx

Logic

100M Rx

Logic

DSP System:

Clock

Data Recovery

Equalizer

Analog-to-

Digital

100M PLL

Squelch &

Filters

10M PLL

Receive Section

Central

Bias

HP Auto-MDIX

Management

Control

SMI

RMII

/ MII L

o

g

ic

TXP / TXN

TXD[0:3]

TXEN

TXER

TXCLK

RXD[0:3]

RXDV

RXER

RXCLK

CRS

COL/CRS_DV

MDC

MDIO

LED1

LED2

LED Circuitry

MODE Control

nINT

nRST

RXP / RXN

10M Tx

Logic

10M

Transmitter

100M Tx

Logic

100M

Transmitter

Transmit Section

PLL

XTAL1/CLKIN

XTAL2

MODE0

MODE1

MODE2

PHY

Address

Latches

PHYAD[0:2]

Auto-

Negotiation

Interrupt

Generator

RMIISEL

MDIX

Control

Reset

Control

RBIAS

This manual is related to the following products: