Table 4-3. set 1, bank 1 registers – Samsung S3C8275X User Manual

Page 73

S3C8275X/F8275X/C8278X/F8278X/C8274X/F8274X

CONTROL

REGISTER

4-3

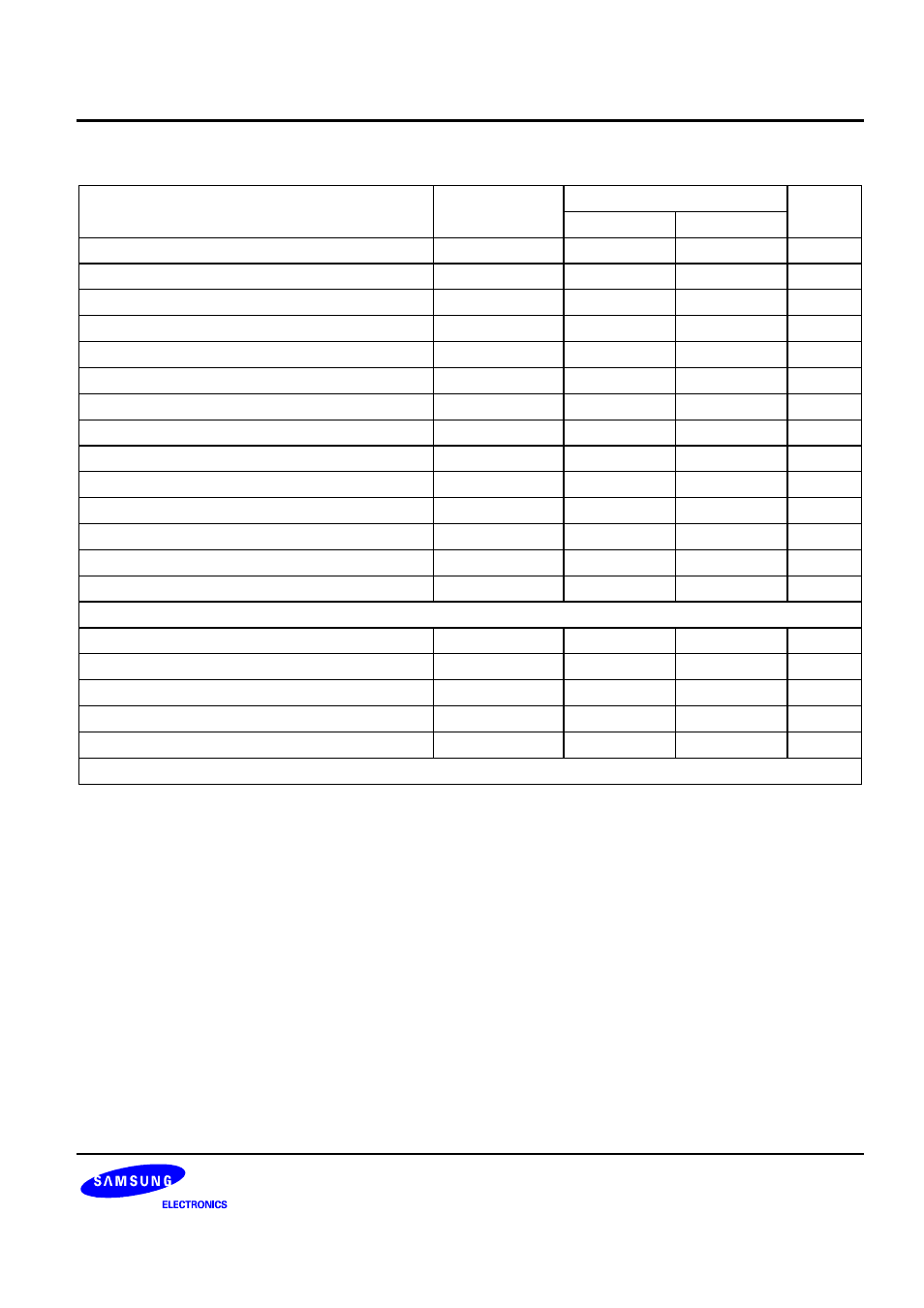

Table 4-3. Set 1, Bank 1 Registers

Register Name

Mnemonic

Address

R/W

Decimal

Hex

LCD control Register

LCON

224

E0H

R/W

Watch timer control register

WTCON

225

E1H

R/W

Timer A counter

TACNT

226

E2H

R

Timer B counter

TBCNT

227

E3H

R

Timer A data register

TADATA

228

E4H

R/W

Timer B data register

TBDATA

229

E5H

R/W

Timer 1/A control register

TACON

230

E6H

R/W

Timer B control register

TBCON

231

E7H

R/W

Clock output control register

CLOCON

232

E8H

R/W

Port 4 control register (high byte)

P4CONH

233

E9H

R/W

Port 4 control register (low byte)

P4CONL

234

EAH

R/W

Port 5 control register (high byte)

P5CONH

235

EBH

R/W

Port 5 control register (low byte)

P5CONL

236

ECH

R/W

Port 6 control register

P6CON

237

EDH

R/W

Locations EEH – EFH are not mapped.

Flash memory control register

FMCON

240

F0H

R/W

Flash memory user programming enable register

FMUSR

241

F1H

R/W

Flash memory sector address register (high byte)

FMSECH

242

F2H

R/W

Flash memory sector address register (low byte)

FMSECL

243

F3H

R/W

Battery level detector control register

BLDCON

244

F4H

R/W

Locations E5H – FFH are not mapped.

NOTES:

1. An “x” means that the bit value is undefined following reset.

2. A dash(“–“) means that the bit is neither used nor mapped, but the bit is read as “0”.