Tacon — timer 1/a control register, Tacon – Samsung S3C8275X User Manual

Page 115

S3C8275X/F8275X/C8278X/F8278X/C8274X/F8274X

CONTROL

REGISTER

4-45

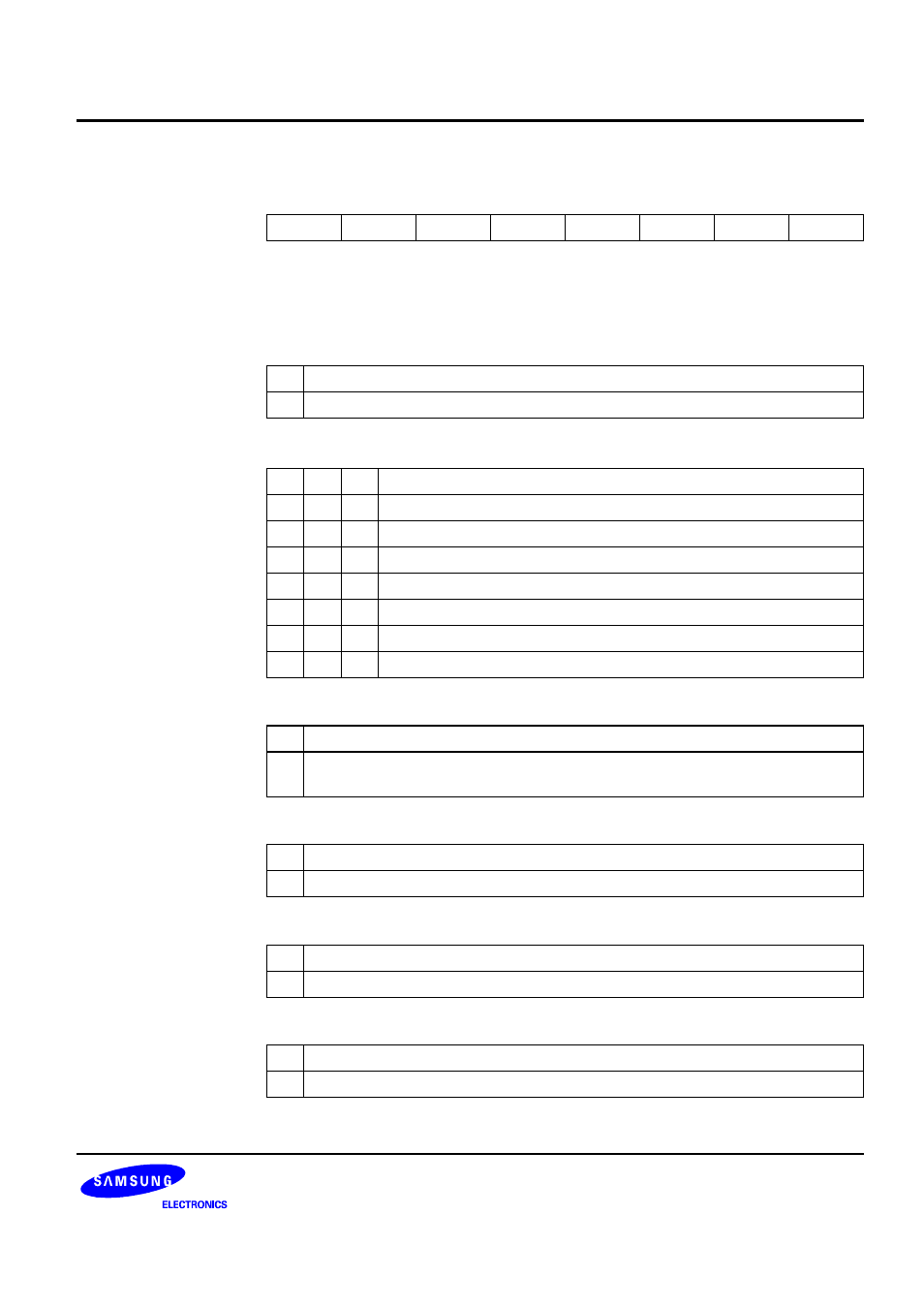

TACON

— Timer 1/A Control Register

E6H

Set 1, Bank 1

Bit

Identifier

.7 .6 .5 .4 .3 .2 .1 .0

Reset Value

0 0 0 0 0 0 0 0

Read/Write

R/W R/W R/W R/W R/W R/W R/W R/W

Addressing Mode

Register addressing mode only

.7

Timer 1 Operating Mode Selection Bit

0

Two 8-bit timers mode (timer A/B)

1

One 16-bit timer mode (timer 1)

.6–.4

Timer 1/A Clock Selection Bits

0 0 0

fxx/512

0 0 1

fxx/256

0 1 0

fxx/64

0 1 1

fxx/8

1 0 0

fxx

(system

clock)

1 0 1

fxt

(sub

clock)

1 1 0

T1CLK

(external

clock)

1 1 1

Not

available

.3

Timer 1/A Counter Clear Bit

0 No

effect

1

Clear the timer 1/A counter (when write, automatically cleared to "0" after being

cleared basic timer counter)

.2

Timer 1/A Counter Operating Enable Bit

0

Disable counting operation

1

Enable counting operation

.1

Timer 1/A Interrupt Enable Bit

0 Disable

interrupt

1 Enable

interrupt

.0

Timer 1/A Interrupt Pending Bit

0

No interrupt pending (when read), clear pending bit (when write)

1

Interrupt is pending (when read)