Host-port interface timing – Motorola TMS320C6711D User Manual

Page 87

TMS320C6711D

FLOATINGĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS292 − OCTOBER 2005

87

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251−1443

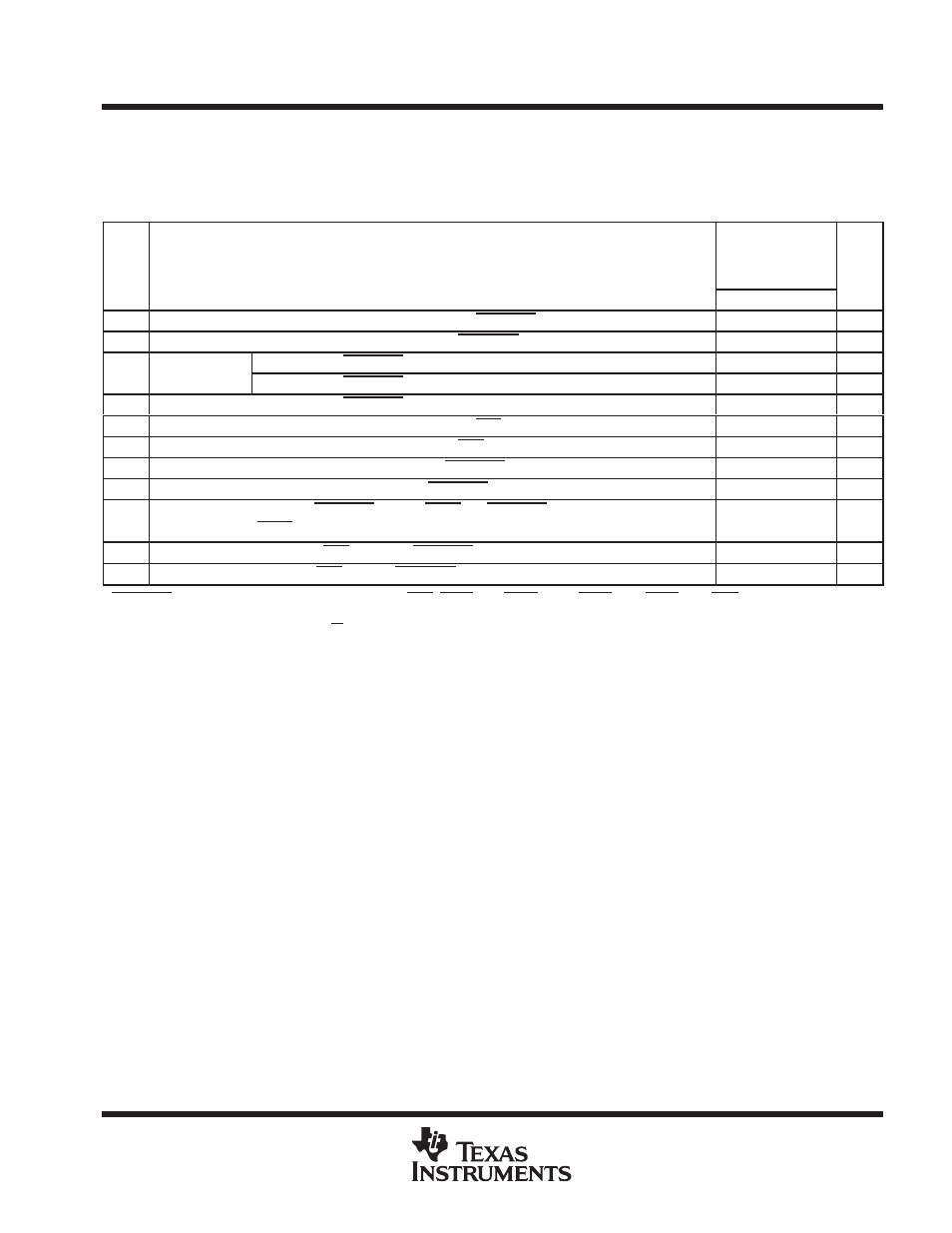

HOST-PORT INTERFACE TIMING

timing requirements for host-port interface cycles

†‡

(see Figure 42, Figure 43, Figure 44, and

Figure 45)

NO.

GDPA−167

ZDPA−167

−200

−250

UNIT

MIN

MAX

1

tsu(SELV-HSTBL) Setup time, select signals§ valid before HSTROBE low

5

ns

2

th(HSTBL-SELV) Hold time, select signals§ valid after HSTROBE low

4

ns

3

tw(HSTBL)

Pulse duration, HSTROBE low (host read access)

4P

ns

3

tw(HSTBL)

Pulse duration, HSTROBE low (host write access)

4P

ns

4

tw(HSTBH)

Pulse duration, HSTROBE high between consecutive accesses

4P

ns

10

tsu(SELV-HASL) Setup time, select signals§ valid before HAS low

5

ns

11

th(HASL-SELV)

Hold time, select signals§ valid after HAS low

3

ns

12

tsu(HDV-HSTBH) Setup time, host data valid before HSTROBE high

5

ns

13

th(HSTBH-HDV) Hold time, host data valid after HSTROBE high

3

ns

14

th(HRDYL-HSTBL)

Hold time, HSTROBE low after HRDY low. HSTROBE should not be inactivated until

HRDY is active (low); otherwise, HPI writes will not complete properly.

2

ns

18

tsu(HASL-HSTBL) Setup time, HAS low before HSTROBE low

2

ns

19

th(HSTBL-HASL) Hold time, HAS low after HSTROBE low

2

ns

† HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

‡ P = 1/CPU clock frequency in ns. For example, when running parts at 250 MHz, use P = 4 ns.

§ Select signals include: HCNTL[1:0], HR/W, and HHWIL.