Reset timing (continued) – Motorola TMS320C6711D User Manual

Page 85

TMS320C6711D

FLOATINGĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS292A − OCTOBER 2005 − REVISED NOVEMBER 2005

85

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251−1443

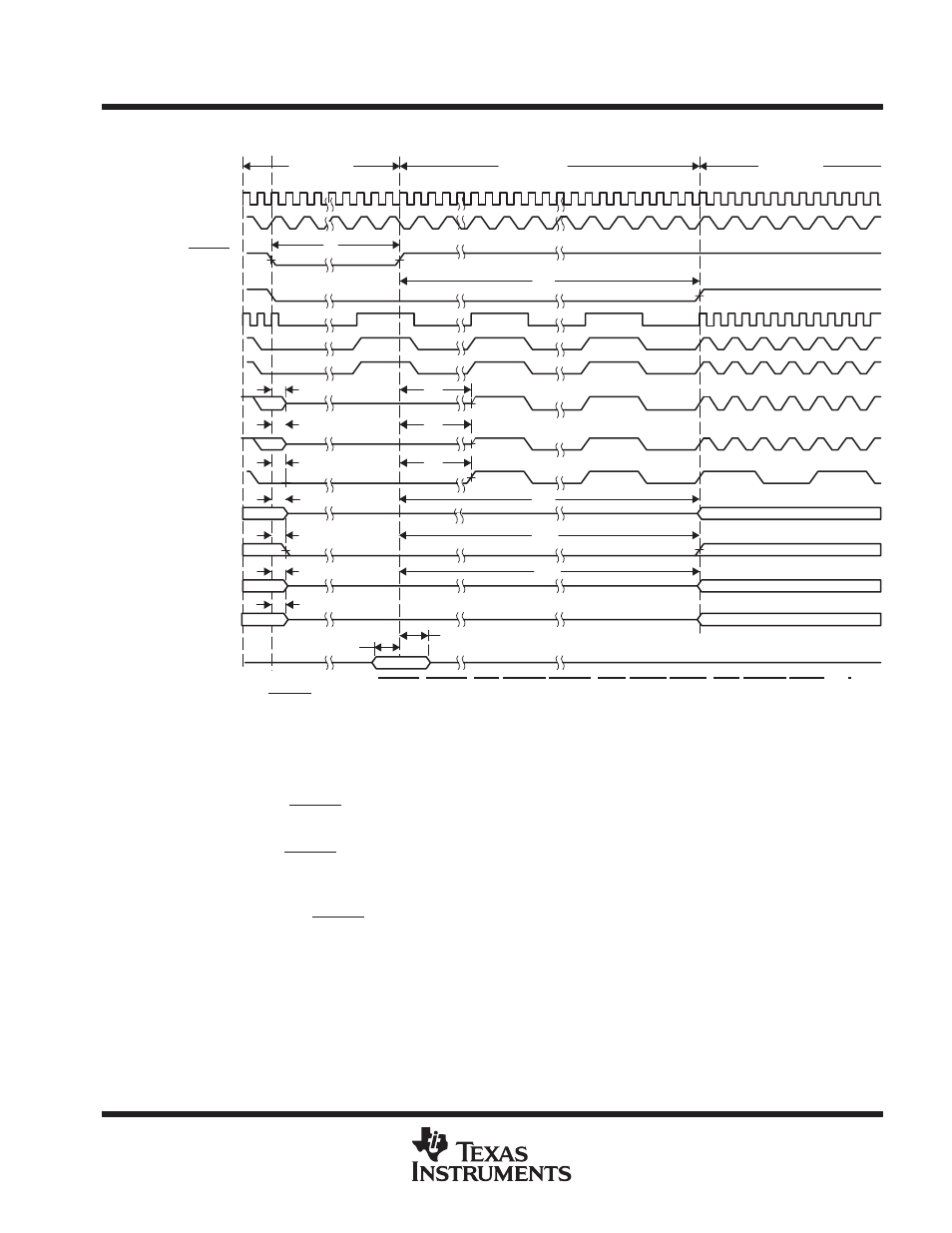

RESET TIMING (CONTINUED)

Phase 1

Phase 2

11

10

9

8

7

6

5

4

3

14

13

2

1

1

CLKIN

ECLKIN

Internal Reset

Internal SYSCLK1

Internal SYSCLK2

Internal SYSCLK3

RESET

Phase 3

EMIF Z Group†

EMIF Low Group†

Z Group†

Boot and Device

Configuration Pins‡

2

2

2

CLKOUT3

ECLKOUT

CLKOUT2

12

Z Group 2†

† EMIF Z group consists of:

EA[21:2], ED[31:0], CE[3:0], BE[3:0], ARE/SDCAS/SSADS, AWE/SDWE/SSWE, AOE/SDRAS/SSOE and

HOLDA

EMIF low group consists of: BUSREQ

Z group 1 consists of:

CLKR0, CLKR1, CLKX0, CLKX1, FSR0, FSR1, FSX0, FSX1, DX0, DX1, TOUT0, and TOUT1.

Z group 2 consists of:

All other HPI and GPIO signals

‡ Boot and device configurations consist of: HD[8, 4:3].

Figure 40. Reset Timing

Reset Phase 1: The RESET pin is asserted. During this time, all internal clocks are running at the CLKIN

frequency divide-by-8. The CPU is also running at the CLKIN frequency divide-by-8.

Reset Phase 2: The RESET pin is deasserted but the internal reset is stretched. During this time, all internal

clocks are running at the CLKIN frequency divide-by-8. The CPU is also running at the CLKIN frequency

divide-by-8.

Reset Phase 3: Both the RESET pin and internal reset are deasserted. During this time, all internal clocks are

running at their default divide-down frequency of CLKIN. The CPU clock (SYSCLK1) is running at CLKIN

frequency. The peripheral clock (SYSCLK2) is running at CLKIN frequency divide-by-2. The EMIF internal clock

source (SYSCLK3) is running at CLKIN frequency divide-by-2. SYSCLK3 is reflected on the ECLKOUT pin

(when EKSRC bit = 0 [default]). CLKOUT3 is running at CLKIN frequency divide-by-8.