1 instruction decoding, 2 .1 instruction decoding -2, Figure 2-1 . instruction word format -2 – Maxim Integrated MAX31782 User Manual

Page 6: 1instructiondecoding

MaximIntegrated 2-2

MAX31782 User’s Guide

Revision 0; 8/11

SECTION 2: ARCHITECTURE

The MAX31782 contains a MAXQ20 low-cost, high-performance, CMOS, fully static microcontroller with flash memory .

It is structured on a highly advanced, 16-accumulator-based, 16-bit RISC architecture . Fetch and execution operations

are completed in one cycle without pipelining, since the instruction contains both the op code and data . The highly

efficient core is supported by 16 accumulators and a 16-level hardware stack, enabling fast subroutine calling and task

switching .

Data can be quickly and efficiently manipulated with three internal data pointers . Two of these data pointers, DP0 and

DP1, are stand-alone 16-bit pointers . The third data pointer, frame pointer, is composed of a 16-bit base pointer (BP)

and an 8-bit offset register (OFFS) . All three pointers support postincrement/decrement functionality for read operations

and preincrement/decrement for write operations . For the frame pointer (FP = BP[OFFS]), the increment/decrement

operation is executed on the OFFS register and does not affect the base pointer . Multiple data pointers allow more than

one function to access data memory without having to save and restore data pointers each time .

Stack functionality is provided by dedicated memory with a 16-bit width and a depth of 16 . An on-chip memory manage-

ment unit (MMU) allows logical remapping of the program and data spaces, and thus facilitates in-system programming

and fast access to data tables, arrays, and constants located in flash memory .

This section provides details on the following topics .

1) Instruction decoding

2) Register space

3) Memory types

4) Program and data memory mapping and access

5) Data alignment

6) Reset conditions

7) Clock generation

8) Power modes

2.1InstructionDecoding

The MAX31782 uses the standard 16-bit MAXQ20 core instruction set, which is described in

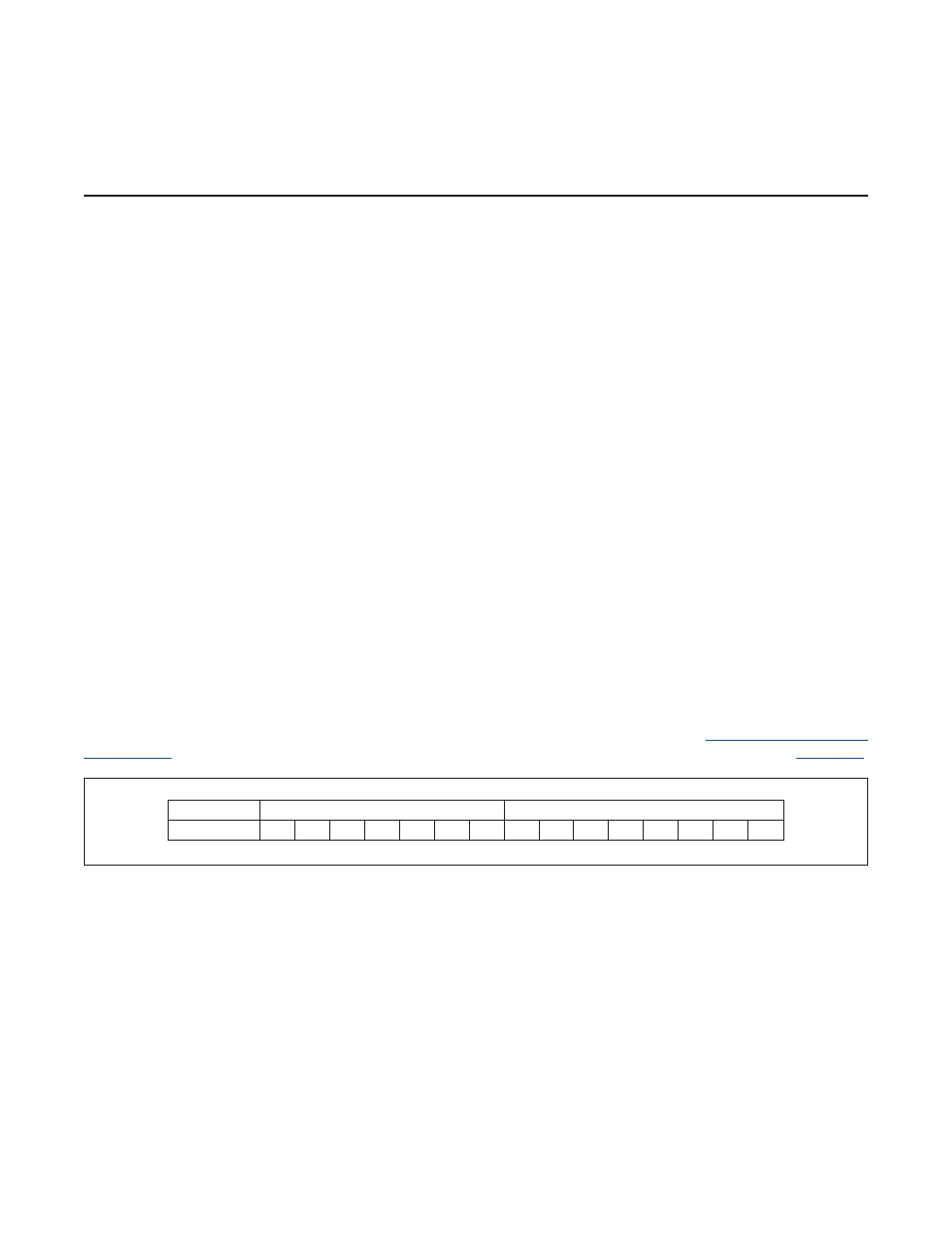

. Every instruction is encoded as a single 16-bit word . The instruction word format is shown in

Figure 2-1. Instruction Word Format

Bit 15 (f) indicates the format for the source field of the instruction as follows:

If f equals 0, the instruction is an immediate source instruction . The source field represents an immediate 8-bit value .

If f equals 1, the instruction is a register source instruction . The source field represents the register from which the

source value is read .

Bits 14 to 8 (ddddddd) represent the destination for the transfer . This value always represents a destination register . The

lower four bits contain the module specifier and the upper three bits contain the register index in that module .

Bits 7 to 0 (ssssssss) represent the source for the transfer . Depending on the value of the format field, this can either

be an immediate value or a source register . If this field represents a register, the lower four bits contain the module

specifier and the upper four bits contain the register index in that module .

FORMAT

DESTINATION

SOURCE

f

d

d

d

d

d

d

d

s

s

s

s

s

s

s

s