7 in-circuit debug data register (icdd, m2[1eh]), 7in-circuitdebugdataregister(icdd,m2[1eh]), Maximintegrated 17-16 – Maxim Integrated MAX31782 User Manual

Page 151

MaximIntegrated 17-16

MAX31782 User’s Guide

Revision 0; 8/11

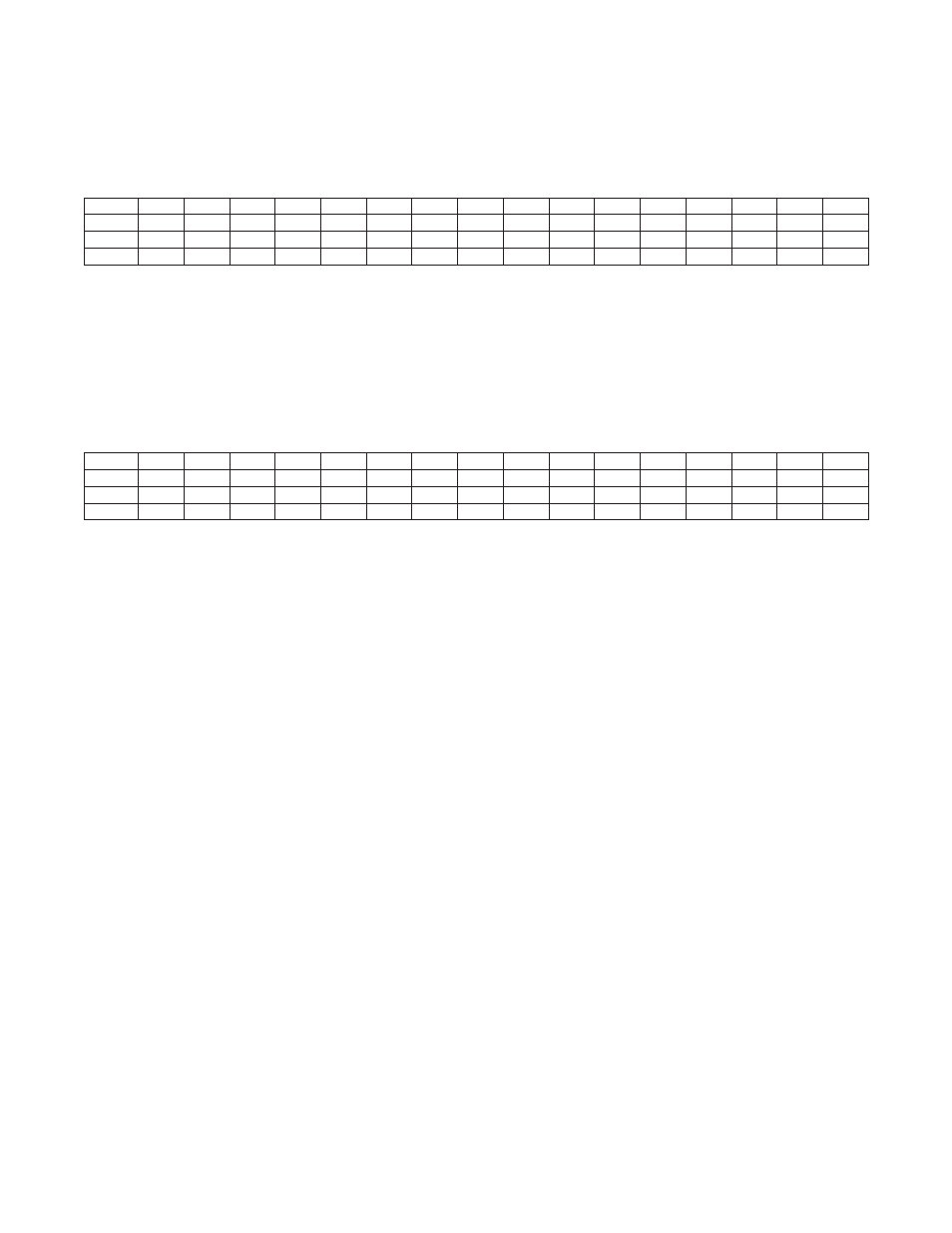

17.3.6In-CircuitDebugAddressRegister(ICDA,M2[1Dh])

This register is used by the debug engine to store addresses so that ROM code can view that information . This register

is also used by the debug engine as a mask register to mask out don’t care bits in the ICDD register when BP5 is used

as a register breakpoint . When a bit in this register is set to 1, the corresponding bit location in the ICDD register is

compared to the data being written to the destination register to determine if a break should be generated . When a bit

in this register is cleared, the corresponding bit in the ICDD register becomes a don’t care and is not compared against

the data being written . When all bits in this register are cleared, any updated data pattern causes a break when the BP5

register matches the destination register address of the current instruction .

17.3.7In-CircuitDebugDataRegister(ICDD,M2[1Eh])

This register is used by the debug engine to store data or read count so that ROM code can view that information .

This register is also used by the debug engine as a data register for content matching when BP5 is used as a register

breakpoint . In this case, only data bits in this register with their corresponding mask bits in the ICDA register set are

compared with the updated destination data to determine if a break should be generated .

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

ICDA .15 ICDA .14 ICDA .13 ICDA .12 ICDA .11 ICDA .10

ICDA .9

ICDA .8

ICDA .7

ICDA .6

ICDA .5

ICDA .4

ICDA .3

ICDA .2

ICDA .1

ICDA .0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

ICDD .15 ICDD .14 ICDD .13 ICDD .12 ICDD .11 ICDD .10

ICDD .9

ICDD .8

ICDD .7

ICDD .6

ICDD .5

ICDD .4

ICDD .3

ICDD .2

ICDD .1

ICDD .0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r