3 processor status flags register (psf, 8h[4h]), 4 interrupt and control register (ic, 8h[5h]), 3processorstatusflagsregister(psf,8h[4h]) – Maxim Integrated MAX31782 User Manual

Page 23: 4interruptandcontrolregister(ic,8h[5h])

MaximIntegrated 3-5

MAX31782 User’s Guide

Revision 0; 8/11

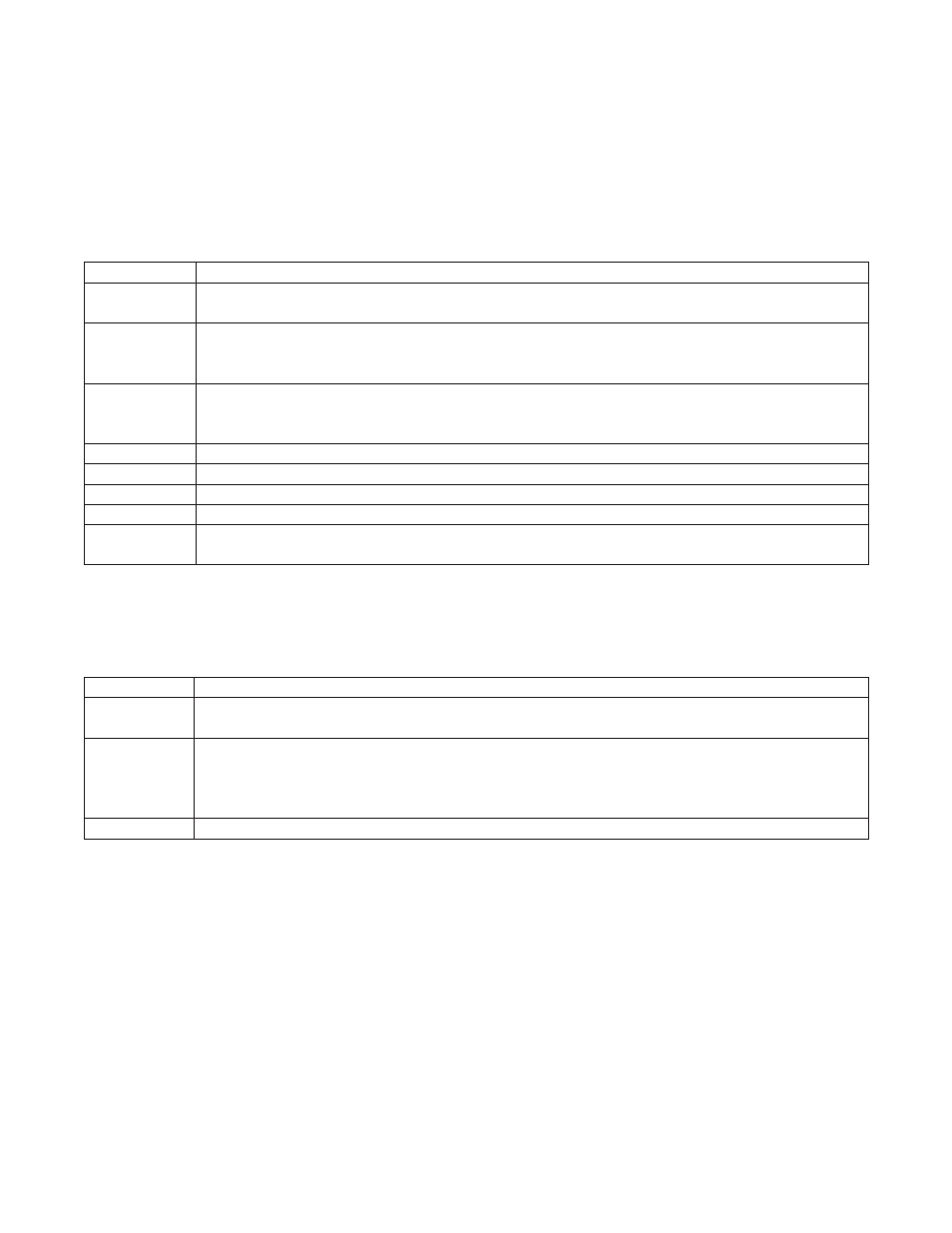

3.1.3ProcessorStatusFlagsRegister(PSF,8h[4h])

Initialization: This register is cleared to 80h on all forms of reset .

Access: Bit 7 (Z), bit 6 (S), and bit 2 (OV) are read-only . Bits 4 and 3 (GPF1, GPF0), bit 1 (C), and bit 0 (E) are unre-

stricted read/write .

3.1.4InterruptandControlRegister(IC,8h[5h])

Initialization: This register is cleared to 00h on all forms of reset .

Access: Unrestricted direct read/write access .

BIT

FUNCTION

PSF .0 (E)

Equals Flag . This bit flag is set to 1 whenever a compare operation (CMP) returns an equal result . If a CMP

operation returns not equal, this bit is cleared .

PSF .1 (C)

Carry Flag . This bit flag is set to 1 whenever an add or subtract operation (ADD, ADDC, SUB, SUBB) returns a

carry or borrow . This bit flag is cleared to 0 whenever an add or subtract operation does not return a carry or

borrow . Many other instructions potentially affect the carry bit .

PSF .2 (OV)

Overflow Flag . This flag is set to 1 if there is a carry out of bit 14 but not out of bit 15, or a carry out of bit 15 but

not out of bit 14 from the last arithmetic operation, otherwise, the OV flag remains as 0 . OV indicates a negative

number resulted as the sum of two positive operands, or a positive sum resulted from two negative operands .

PSF .3 (GPF0)

General-Purpose Flag 0

PSF .4 (GPF1)

General-Purpose Flag 1 . These general-purpose flag bits are provided for user software control .

PSF .5

Reserved . All reads return 0 .

PSF .6 (S)

Sign Flag . This bit flag mirrors the current value of the high bit of the active accumulator (Acc .15) .

PSF .7 (Z)

Zero Flag . The value of this bit flag equals 1 whenever the active accumulator is equal to zero, and it equals 0

otherwise .

BIT

FUNCTION

IC .0 (IGE)

Interrupt Global Enable . This bit enables the interrupt handler if set to 1 . No interrupt to the CPU is allowed if

this bit is cleared to 0 .

IC .1 (INS)

Interrupt In Service . The INS is set by the interrupt handler automatically when an interrupt is acknowledged .

No further interrupts occur as long as the INS bit remains set . The interrupt service routine can clear the INS bit

to allow interrupt nesting . Otherwise, the INS bit is cleared automatically by the interrupt handler upon execu-

tion of an RETI/POPI instruction .

IC .[7:2]

Reserved . All reads return 0 .