Intel STL2 User Manual

Page 57

STL2 Server Board TPS

Basic Input Output System (BIOS)

Revision 1.0

4-49

•

The 8-bit test point is broken down to four 2-bit groups.

•

Each group is made one-based (1 through 4)

•

One to four beeps are generated based on each group’s 2-bit pattern.

Example:

Checkpoint 04Bh will be broken down to:

01 00 10 11

And the beep code will be:

2 – 1 – 3 – 4

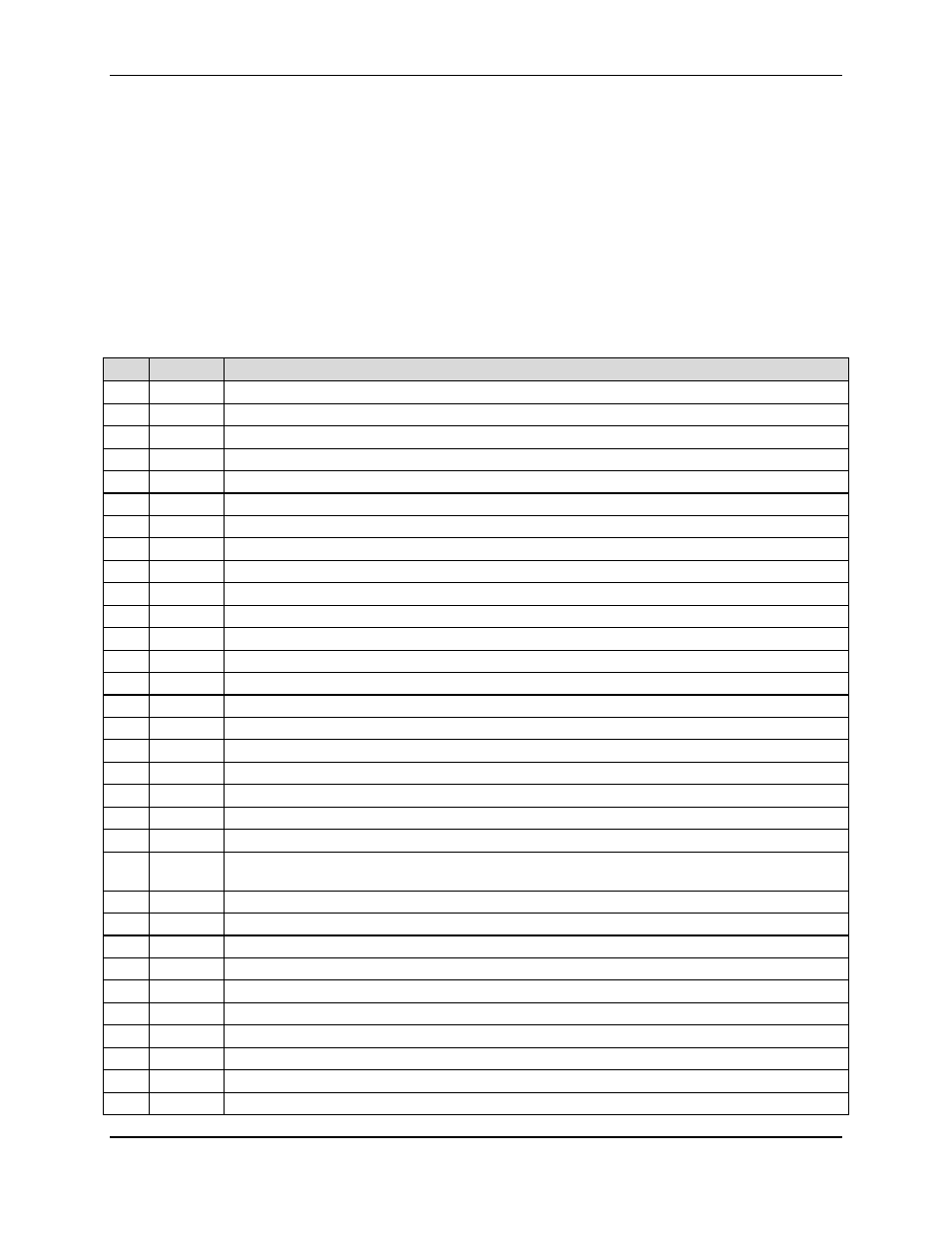

Table 4-24. Standard BIOS Port-80 Codes

CP

Beeps

Reason

02

Verify Real Mode

04

Get Processor type

06

Initialize system hardware

08

Initialize chipset registers with initial POST values

09

Set in POST flag

0A

Initialize Processor registers

0B

Enable Processor cache

0C

Initialize caches to initial POST values

0E

Initialize I/O

0F

Initialize the local bus IDE

10

Initialize Power Management

11

Load alternate registers with initial POST values

12

Restore Processor control word during warm boot

14

Initialize keyboard controller

16

1-2-2-3

BIOS ROM checksum

18

8254 timer initialization

1A

8237 DMA controller initialization

1C

Reset Programmable Interrupt Controller

20

1-3-1-1

Test DRAM refresh

22

1-3-1-3

Test 8742 Keyboard Controller

24

Set ES segment register to 4GB

28

1-3-3-1

Autosize DRAM, system BIOS stops execution here if the BIOS does not detect any usable

memory DIMMs

2A

Clear 8 MB base RAM

2C

1-3-4-1

Base RAM failure, BIOS stops execution here if entire memory is bad

32

Test Processor bus-clock frequency

34

Test CMOS

35

RAM Initialize alternate chipset registers

36

Warm start shut down

37

Reinitialize the chipset

38

Shadow system BIOS ROM

39

Reinitialize the cache

3A

Autosize cache