Intel STL2 User Manual

Page 17

STL2 Server Board TPS

STL2 Server Board Architecture Overview

Revision 1.0

2-9

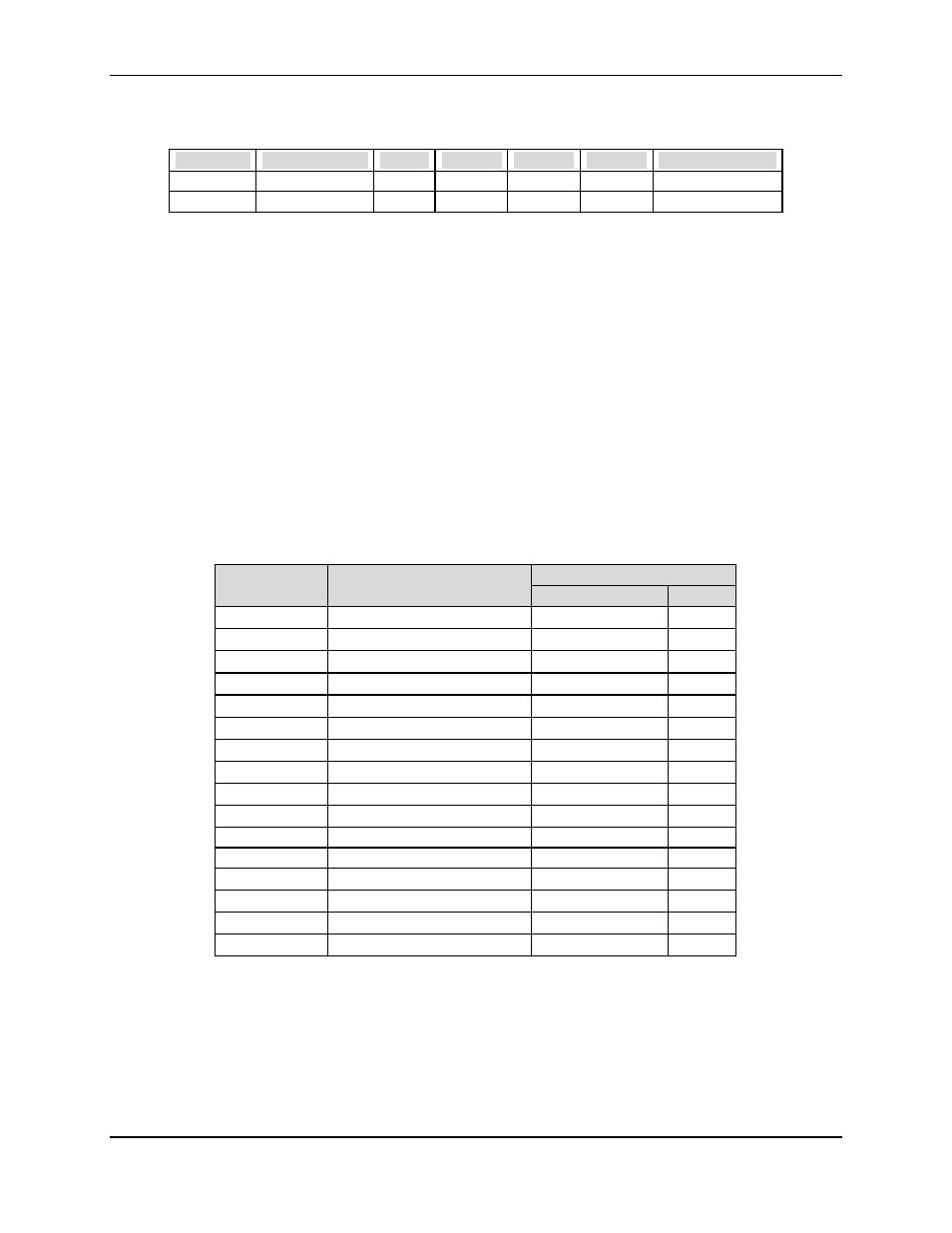

Table 2-2. SCSI Transfer Speeds

SCSI Port

Asynchronous

Fast-5

Fast-10

Fast-20

Fast-40

Fast-80/Ultra160

SE

Yes

yes

yes

yes

no

no

LVD

Yes

yes

yes

yes

yes

yes

In the STL2 server board implementation, channel A provides a 68-pin, 16-bit LVD Ultra160

SCSI interface. Channel B provides a 68-pin, 16-bit Single Ended Ultra Wide SCSI interface.

Each controller has its own set of PCI configuration registers and SCSI I/O registers. As a PCI

2.1/2.2 bus master, the AIC-7899 supports burst data transfers on PCI up to the maximum rate

of 133 MBps using on-chip buffers.

Refer to the AIC-7899 PCI-Dual Channel SCSI Multi-Function Controller Data Manual for more

information on the internal operation of this device and for descriptions of SCSI I/O registers.

2.4.1.1.1 AIC-7899 Supported PCI Commands

The AIC-7899 supports PCI commands as shown in the following table:

Table 2-3. Embedded SCSI Supported PCI Commands

AIC-7899 Support

C/BE [3::0] _L

Command

Target

Master

0000

Interrupt Acknowledge

No

1

No

0001

Special Cycle

No

1

No

0010

I/O Read

Yes

2

No

0011

I/O Write

Yes

2

No

0100

Reserved

No

1

No

0101

Reserved

No

1

No

0110

Memory Read

Yes

2, 3

Yes

4

0111

Memory Write

Yes

2

Yes

4

1000

Reserved

No

1

No

1001

Reserved

No

1

No

1010

Configuration Read

Yes

No

1011

Configuration Write

Yes

No

1100

Memory Read Multiple

Yes

5

Yes

4

1101

Dual Address Cycle

Yes

6

Yes

1110

Memory Read Line

Yes

5

Yes

4

1111

Memory Write and Invalidate

Yes

7

Yes

Notes:

1. Ignored after checking address parity.

2. Support for 8-bit transfers only for all registers in its device register space.

3. Support for 32-bit transfers only for the external ROM/ EEPROM.

4. Support for transfers from system memory.

5. Defaults to Memory Read.

6. Will respond to DAC if PCI Address matches the MBAR[63:12].