Eurotech Appliances VIPER / VIPER-LITE PXA255 User Manual

Page 68

VIPER Technical Manual

Detailed hardware description

© 2007 Eurotech Ltd Issue E

68

VIPER PC/104 interface details

The PC/104 bus signals are compatible with the ISA bus electrical timing definitions.

For details of PC/104 Interrupts please see

All signals (except interrupts) between the PXA255 and the PC/104 are buffered. The

interrupts are connected and processed by CPLD. When the PC/104 bus is not in use

all output signals, with the exception of the clock signals, are set to their inactive state.

The VIPER provides +5V to a PC/104 add-on board via the PL11 and PL12

connectors. If a PC/104 add-on board requires a +12V supply, then +12V must be

supplied to the VIPER power connector PL16 pin 4. If –12V or –5V are required, these

must be supplied directly to the PC/104 add-on board.

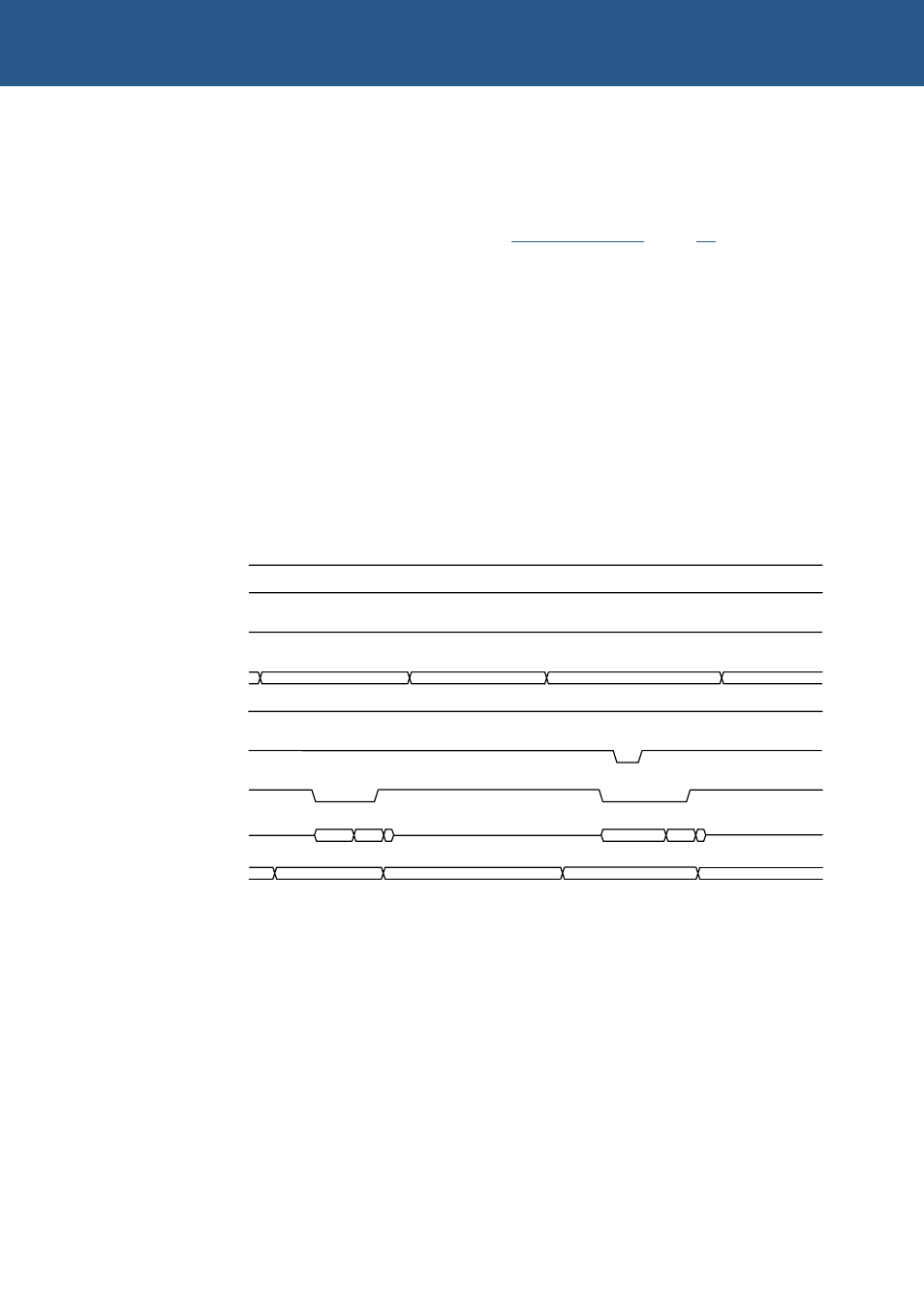

The following diagrams show the activity of the VIPER PC/104 interface for 8 and 16-

bit I/O and memory space accesses.

PC/104 8-bit I/O read/write access cycles

AEN

BALE

SBHE

A<0:15>

IOCS16

IOCHRDY

IOR/IOW

DATA (read)

DATA (write)

VALID

VALID

VALID

VALID

VALID

VALID