Chapter 13 interrupts – Remote Processing RPC-2350 User Manual

Page 56

CHAPTER 13

INTERRUPTS

13-1

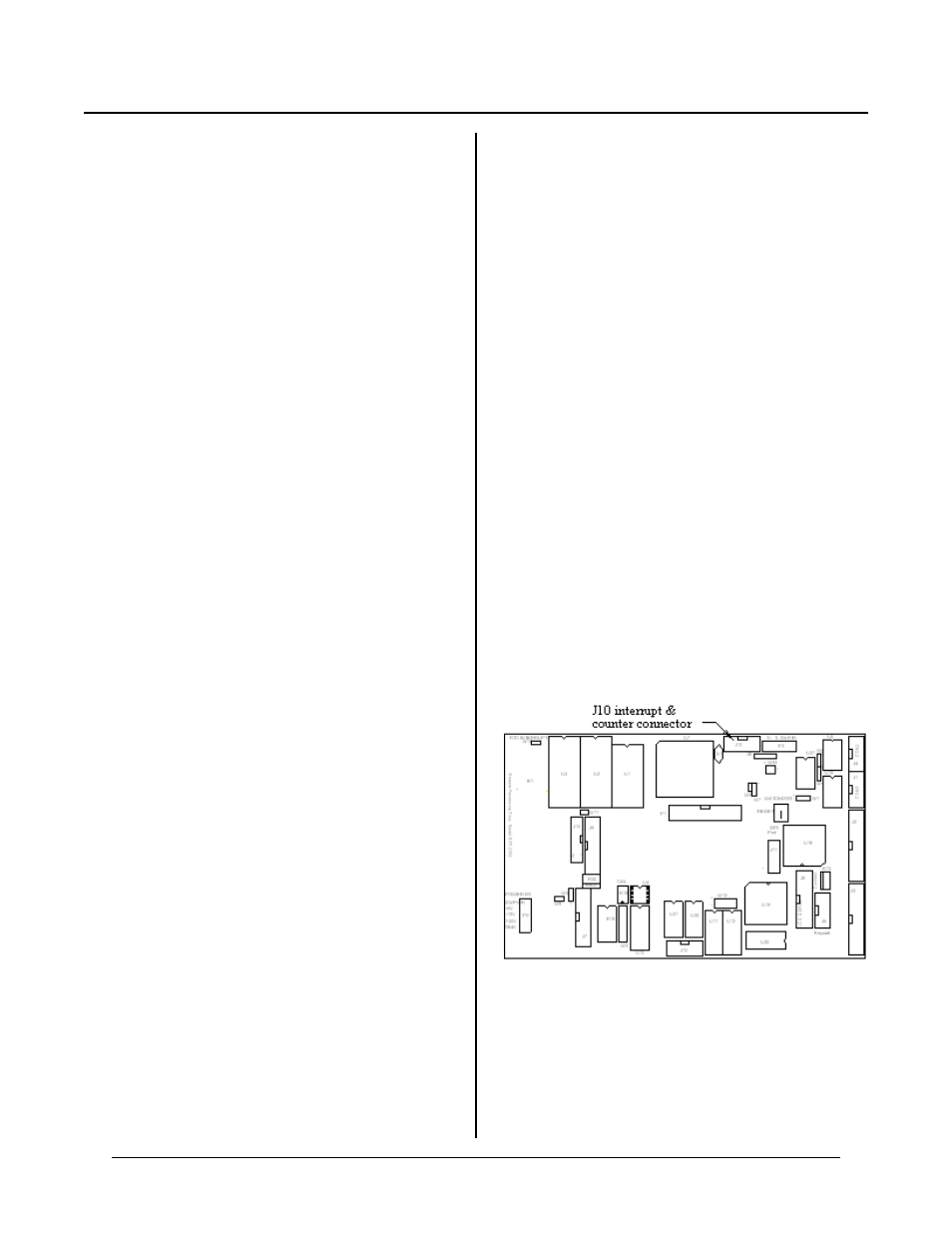

Figure 13-1 J10 and INT 1 location

CHAPTER SYNOPSIS

Discusses types of inter rupts

Interr upt prior ity

DESCRIPTION

INTER RUPT S CHAP TER 13

Interrupts on the RPC-2350 can be broken down into two

general groups: Hardware and software. Hardware

interr upts are IN T 0 and IN T 1. Softwar e interr upts

include ON CO M$, ON TIC K, ON KEYPA D, and

others that require software to execute.

Technically, timer and com munications are also

hardware interr upts. These are suppor ted through

software, and are consider ed software inter rupts.

The NM I hardware interr upt is brought out to the

expansion connector. It is not supported by

CAM BASIC. It is accessible by assembly language.

INTERRUPT HANDLING BY CAMBASIC

Interrupt generating and handling is a bit complex.

First, the gener al rule is exp lained then the e xceptions to

the rules are given.

When INT 0 and INT 1 lines go low, a CPU hardware

interrupt is generated. Softwar e responds by setting a

flag. When the current CAM BASIC line is finished

executing, the line num ber spec ified in ON INT is

executed as a subroutine. Latency depends upon the

complexity of the current CAM BASIC line being

processed and when the interrupt occurr ed while the line

was processed. Typical latency is about 1 mS.

Software interrupts such as ON BIT, ON KEY PAD , and

ON INP require software processing. These routines

scan I/O lines every system tick time (0.005 seconds).

If a condition is met (keypad press, line changes status) a

flag is set. Now, here is w here thing s get a bit

complicated.

The above interrupt tasks are checked every 8 program

line statements (typically 0.005 seconds). T his means

that respon se to a line chang e could take a n additional 5

milli-seconds from the time the event took place.

Hardw are interrupts are the exception. T he operating

system is forced to process these interrupts on the next

statemen t.

What happens when interrupts occur simultaneously?

There is an order of pr iority:

INT 0

INT 1

ON BIT 0 to

ON BIT 7

ON KEYPAD

ON T ICK 0 to

ON TIC K 2

ON C OM$ 1

ON C OM$ 0

ON C OUN T 0 to

ON COUNT 7

ON INP 0 to

ON INP 7

If two interrupts happen simultaneously, they will be

checked and started in this order. U nless you use the

LOC K command, the next interrupt will not be

processed for 8 commands. This means you can have an

interrupt processing routine interrupt another, which can

interrupt another. Since these are all subroutines, the

numbe r you ca n have active at one time is lim ited only

by the amount of available RAM.

Interrupt service routines should be written as short as

possible. Only those lines necessary to stop or start

something should be processed. Heavy duty analysis and

process ing should be do ne in a non-tim e critical loop , if

at all possible.

HARDWARE INTERRUPTS

H a r d wa r e in te r r up ts su p po r te d by C A M BA S IC a r e IN T

0 and INT 1. The r eal time clock uses INT 0, jumpered

via W10. (See Chapter 7). The counter/quadrature

encoder uses INT 1 (See Chapter 14). INT 1 also goes

to J10-2 for external interrupts. Be sure to rem ove any