Verilink TAC 2130 S/T (880-503296-001) Product Manual User Manual

Page 35

Configuration

Verilink TAC 2130 User Manual

3-13

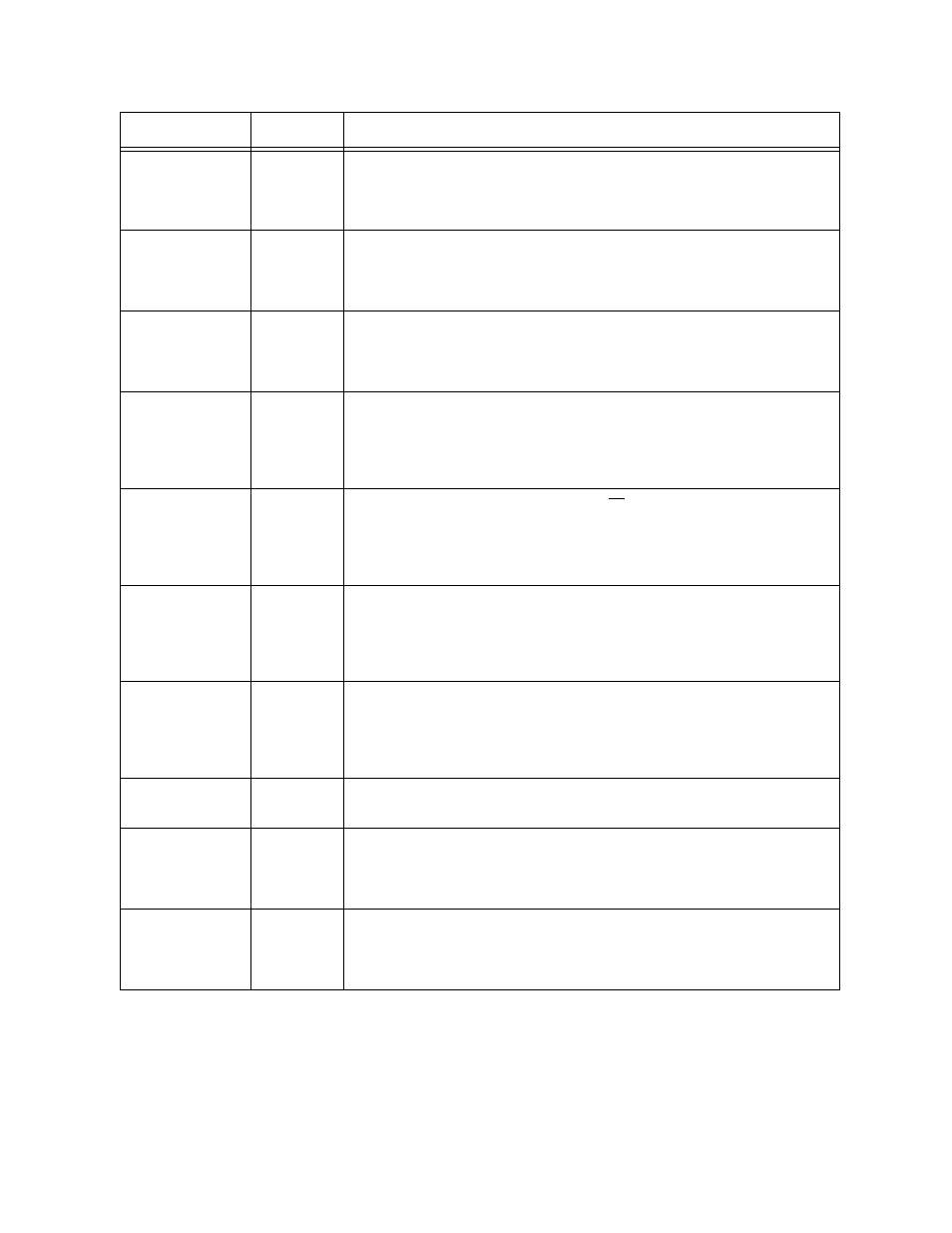

85

DIU 2130

NCC 2130

SCC 2130

TAC 2130

Canned configuration #5—assigns timeslots 1-4 to data port #1 and

timeslots 5-8 to data port #2 (data port #2 ignored by TAC 2130).

86

DIU 2130

NCC 2130

SCC 2130

TAC 2130

Canned configuration #6—assigns timeslots 1-2 to data port #1 and

timeslots 3-4 to data port #2 (data port #2 ignored by TAC 2130).

87

DIU 2130

NCC 2130

SCC 2130

TAC 2130

Canned configuration #7—assigns timeslots 1-23 to data port #1 and

timeslot 24 to data port #2 (data port #2 ignored by TAC 2130).

88

DIU 2130

NCC 2130

SCC 2130

TAC 2130

DIU 2131

Sets DTE port(s) clock to TT. The data port samples Transmit Data

during the negative going transition of a clock received from the DTE

(on the pair Terminal Timing in RS-422, SCTE in V.35, or XTC in RS-

232).

89

DIU 2130

NCC 2130

SCC 2130

TAC 2130

DIU 2131

Sets DTE port(s) clock to inverted ST (ST). The data port samples

Transmit Data during the positive going transition of the transmit

clock signal.

90

DIU 2130

NCC 2130

SCC 2130

TAC 2130

DIU 2131

Sets DTE ports to n

×

56 kbit/s (as required for an AMI T1).

91

DIU 2130

NCC 2130

SCC 2130

TAC 2130

DIU 2131

Unassigns Port 1 timeslot(s).

92 DIU

2130

DIU2131

Unassigns Port 2 timeslot(s).

99

NCC 2020

NCC 2130

SCC 2020

SCC 2130

Resets password for the Craft interface to the default condition (no

password).

00

ALL

Clears the address command. Releases currently selected module. Use

this command if you change your mind after selecting a module in

step two, or if you select the wrong module accidentally, or to practice

double-clicking.

Code

Applies to

Description