Adc chab register 6 0x36 – Sundance SMT941 User Manual

Page 30

User Manual SMT941

Page 30 of 43

Last Edited: 23/08/2011 17:24:00

Default

‘0’

‘0000000’

ADC Chab Register 5 0x35

Setting

Bit 3:0

Description Offset Correction Time Constant (number of clock cycles) ChA

0

‘0000’

256k

1

‘0001’

512k

2

‘0010’

1Meg

3

‘0011’

2Meg

4

‘0100’

4Meg

5

‘0101’

8Meg

6

‘0110’

16Meg

7

‘0111’

32Meg

8

‘1000’

64Meg

9

‘1001’

128Meg

10

‘1010’

256Meg

11

‘1011’

512Meg

Setting

Bit 7:4

Description Gain ChA (Common).

0

‘0000’

0dB gain

1

‘0001’

0.5dB gain

2

‘0010’

1.0dB gain

3

‘0011’

1.5dB gain

4

‘0100’

2.0dB gain

5

‘0101’

2.5dB gain

6

‘0110’

3.0dB gain

7

‘0111’

3.5dB gain

8

‘1000’

4.0dB gain

9

‘1001’

4.5dB gain

10

‘1010’

5.0dB gain

11

‘1011’

5.5dB gain

12

‘1100’

6.0dB gain

Setting

Bit 14:8

Description Fine Gain ChA (Common).

0

128 steps for a range of 0.134dB

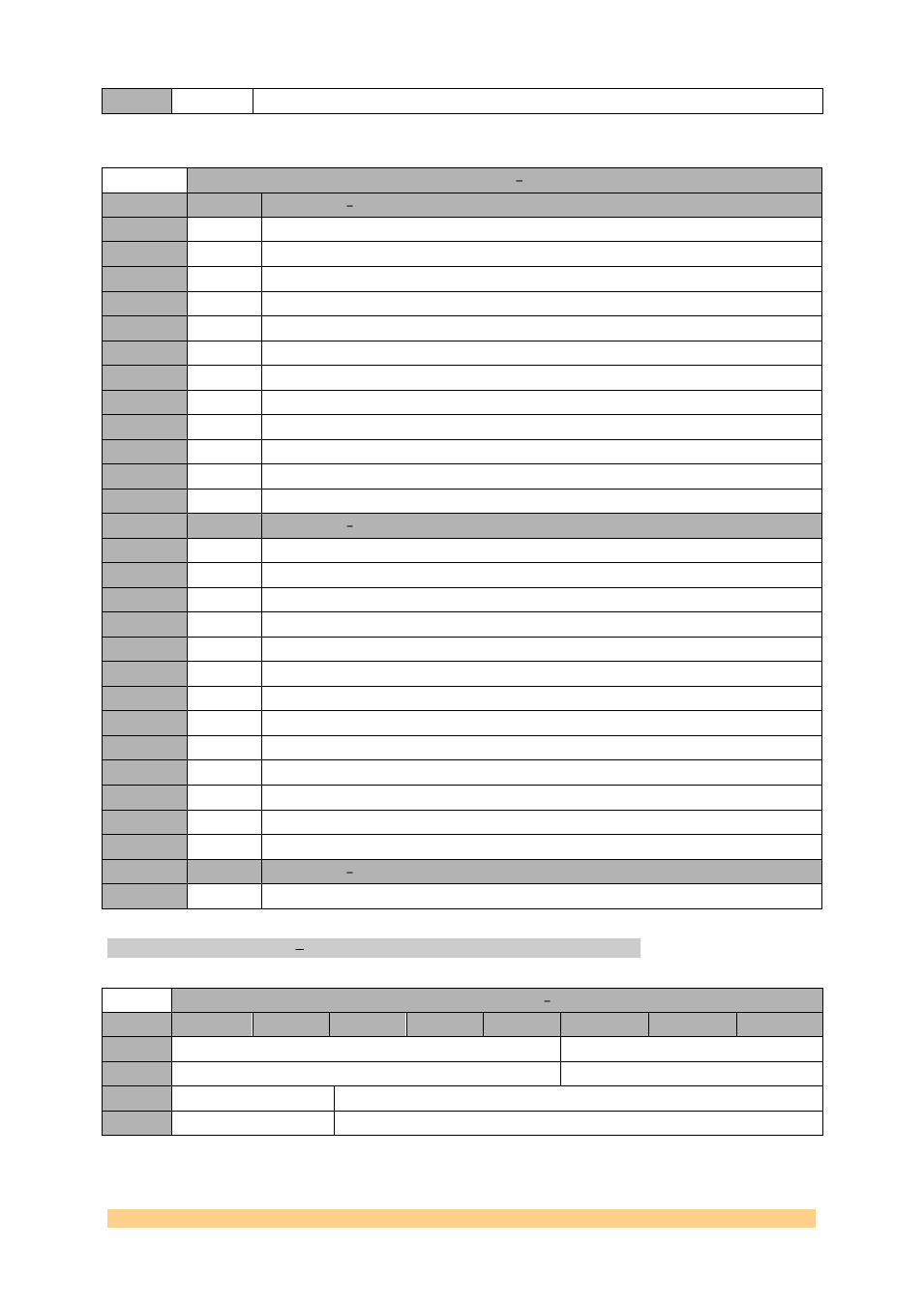

ADC Chab Register 6 0x36.

ADC Chab Register 6 0x36

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Reserved

Test Patterns ChA

Default

‘00000’

‘000’

1

Reserved

Offset Pedestal ChA (Common)

Default

‘00’