1 control packet structure – Sundance SMT941 User Manual

Page 11

User Manual SMT941

Page 11 of 43

Last Edited: 23/08/2011 17:24:00

Input Voltage Level

1 – 3.3 Volts peak-to-peak (AC-coupled)

Frequency Range

0 – 100 MHz.

External Reference Output

Output Voltage Level

1.6 Volts peak-to-peak (AC-coupled)

Output Impedance

50-Ohm (Termination implemented at the

connector)

External Sampling Clock Input

Input Voltage Level

1.5 – 3.3 Volts peak-to-peak (AC-coupled)

Input Format

Single-ended.

Frequency range

10-500 MHz

External Sampling Clock Output

Output Voltage Level

0-2.4 Volts fixed amplitude

Output Format

LVTTL

External Trigger Inputs

Input Voltage Level

1.5-3.3 Volts peak-to-peak.

Format

DC-coupled and Single-ended (Termination

implemented at the connector). Differential

on option (3.3 V PECL).

Impedance

50-Ohm.

Frequency range

62.5 MHz maximum

Delay

External Ref. Input to Ext Ref. Out

External Clk Input to Ext Clk Out

9ns (between J29 and J4)

Figure 3 - Clock Architecture Main Characteristics.

2.3 FPGA Design

2.3.1 Control Register Settings

The Control Registers control the complete functionality of the SMT941. They are

setup via the Comport3 (standard firmware provided). The settings of the ADCs,

triggers, clocks and the configuration of the interfaces and the internal FPGA data

path settings can be configured via the Control Registers.

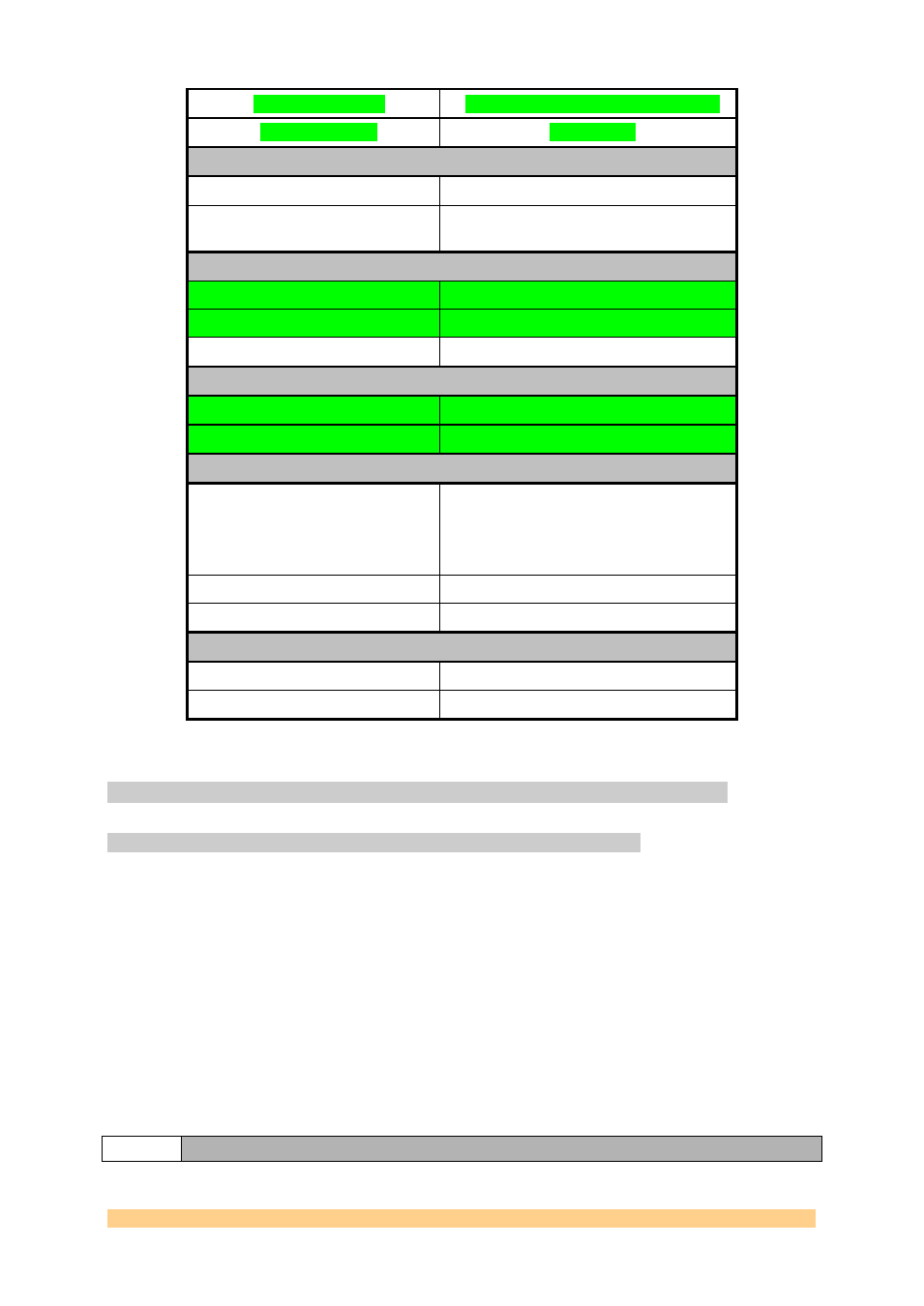

2.3.1.1 Control Packet Structure

The data passed on to the SMT941 over the Comport must conform to a certain

packet structure. Only valid packets will be accepted and only after acceptance of a

packet will the appropriate settings be implemented. Each packet will start with a

command (4 bits – 0x1 for a write operation – 0x2 for a read operation) information,

followed by a register address (12 bits – see table Memory Map), followed by a 16-bit

data. This structure is illustrated in the following figure:

Byte Content