2 registers addresses – Sundance SMT381 2007 User Manual

Page 23

Example 1:

Sending 0x1001FFFF to the task will Write, to Address 0x001, Data FFFF

Example 2:

Sending 0x2801xxxx to the task will request a Read, from Address 0x801. The data will

be written to the output channel 0.

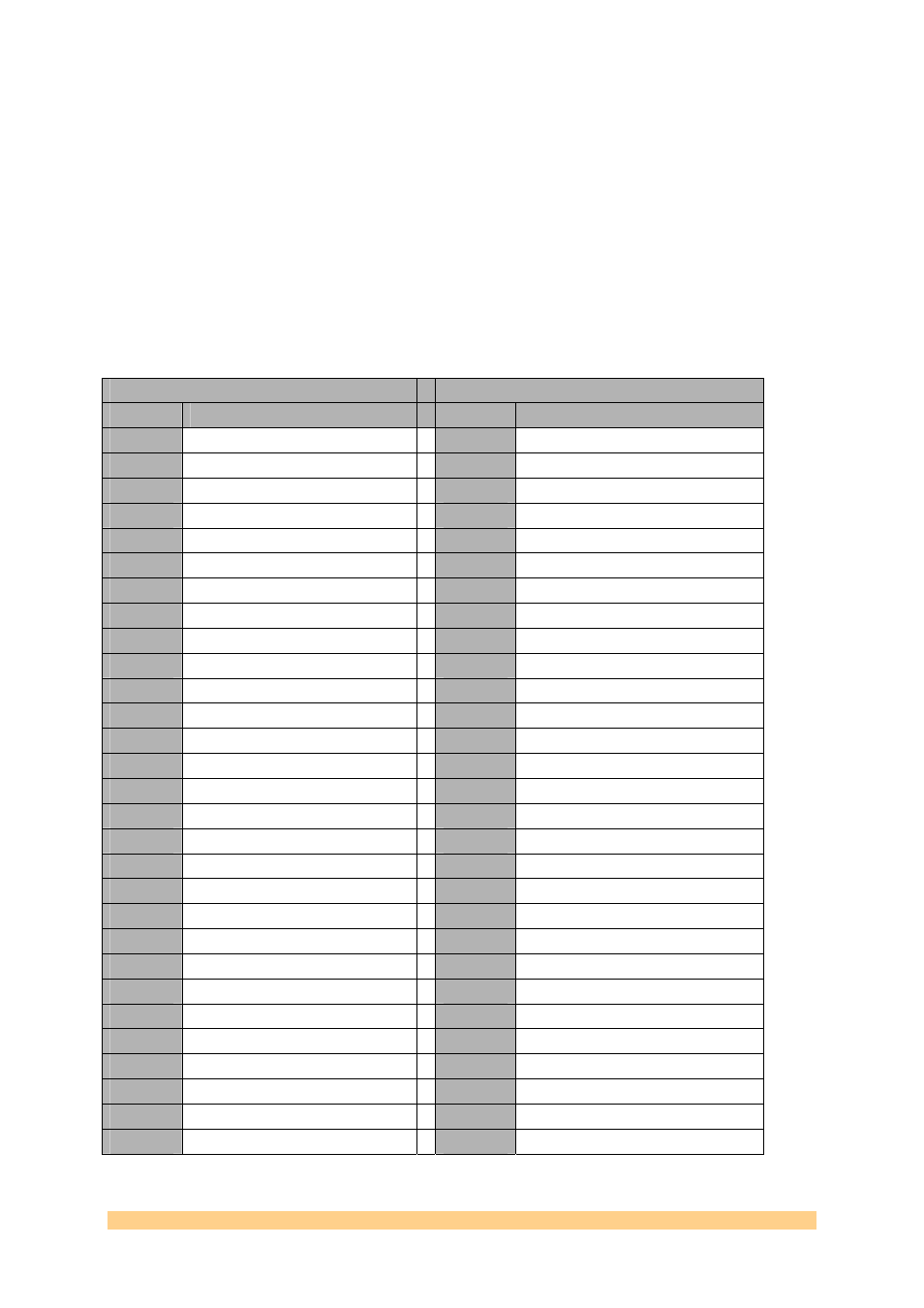

7.1.2.2 Registers addresses

The following figure shows the memory map for registers. Detailed description of the

registers is provided in appendix.

Write Side

Read Side

Address

Register

Address

Register

0x000

Reset Register

0x000 Reserved

0x001 Reserved

0x001 Reserved

0x002 Reserved

0x002 Reserved

0x003 Reserved

0x003 Reserved

0x004 Reserved

0x004 Reserved

0x005

Smt381DacData(LSB)

0x005 Reserved

0x006

Smt381DacData

0x006 Reserved

0x007

Smt381DacData

0x007 Reserved

0x008

Smt381DacData(MSB)

0x008 Reserved

0x009 Smt381DacSetup

0x009 Reserved

0x00A Smt381DacAddress

0x00A Reserved

0x00B

Smt381Pll_IfR_Reg1

0x00B Reserved

0x00C

Smt381Pll_IfR_Reg2

0x00C Reserved

0x00D

Smt381Pll_IfN_Reg1

0x00D Reserved

0x00E

Smt381Pll_IfN_Reg2

0x00E Reserved

0x00F

Smt381Pll_RfR_Reg1

0x00F Reserved

0x010

Smt381Pll_RfR_Reg2

0x010 Reserved

0x011

Smt381Pll_RfN_Reg1

0x011 Reserved

0x012

Smt381Pll_RfN_Reg2 *

0x012 Reserved

0x013

Smt381AdjClkCntrlReg *

0x013 Reserved

0x014

Smt381ClockSourceSelect

0x014 Reserved

0x015 Reserved

0x015 Reserved

0x016 Reserved

0x016 Reserved

0x017 Reserved

0x017 Reserved

0x018 Reserved

0x018 Reserved

0x019 Reserved

0x019 Reserved

0x01A Reserved

0x01A Reserved

0x01B Reserved

0x01B Reserved

0x01C Reserved

0x01C Reserved

User Manual SMT381

Page 23 of 31

Last Edited: 12/06/2007 10:43:00