2 bottom view, 6 pinout, 1 dip switch sw2 – Sundance SMT368 User Manual

Page 21: 2 shb header, 3 jtag header, Bottom view, Pinout, Dip switch sw2, Shb header, Jtag header

Sundance Multiprocessor Technology Limited

Form : QCF42

User Manual

Date : 6 July 2006

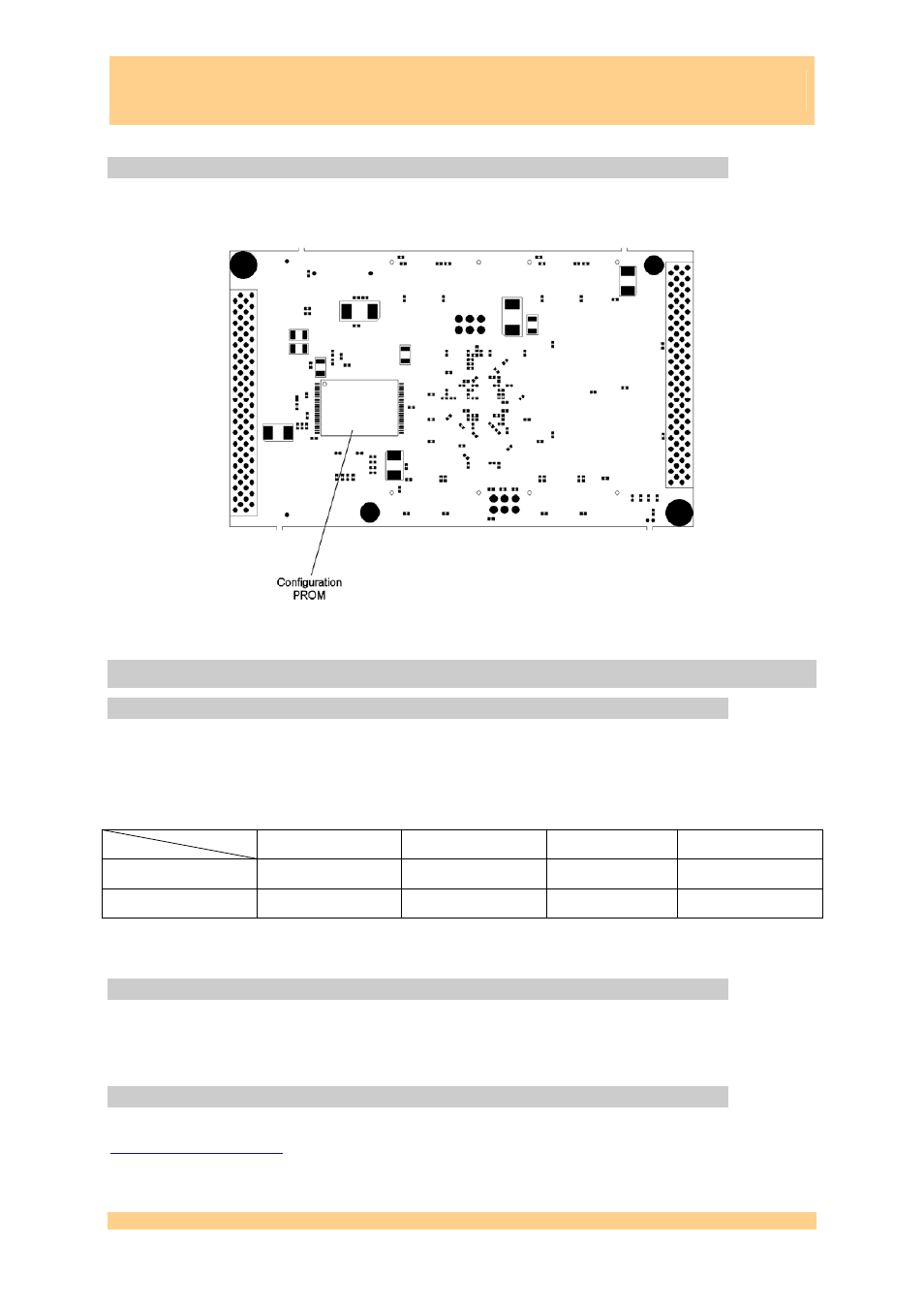

5.2 Bottom View

Figure 14: PCB – Bottom view

6 Pinout

6.1 DIP switch SW2

The DIP switch SW2 is not used in the default firmware. It is therefore connected to the

CPLD for custom applications.

The following table describes the settings for the positions of the SW2:

Configuration

SW2 Pos

POS1 POS2 POS3 POS4

Pin of CPLD

53 52 51 50

Type

I/O I/O I/O I/O

Table 5:SW2 DIP switch settings

6.2 SHB Header

The SHB connectors support LVTTL standard only. They are referenced SHBA, SHBB, SHBC

and SHBD.

6.3 JTAG Header

The JTAG header is a 2mm pitch pin-socket, and it is referenced JP1. It is compliant with the

.

User Manual SMT368

Last Edited: 31/12/2008 13:53:00

- SMT107 (16 pages)

- SMT6035 v.2.2 (39 pages)

- SMT6012 v.4.6 (22 pages)

- FC100 (12 pages)

- FC108 v.1.1 (10 pages)

- SMT6065 v.4.0 (45 pages)

- FFT v.2.1 (19 pages)

- SMT111 (18 pages)

- SMT118LT (10 pages)

- SMT118 (20 pages)

- SMT123-SHB (13 pages)

- SMT128 (15 pages)

- SMT145 (18 pages)

- SMT148 (35 pages)

- SMT130 v.1.0 (46 pages)

- SMT148FX (48 pages)

- SMT310Q (55 pages)

- PARS (70 pages)

- SMT166-FMC (52 pages)

- SMT166 (44 pages)

- SMT300Q v.1.6 (61 pages)

- SMT310 v.1.6 (50 pages)

- SMT317 (24 pages)

- SMT326v2 (24 pages)

- SMT338 (19 pages)

- SMT349 (32 pages)

- SMT339 v.1.3 (27 pages)

- SMT338-VP (22 pages)

- SMT358 (25 pages)

- SMT351T (37 pages)

- SMT351 (25 pages)

- SMT350 (45 pages)

- SMT362 (30 pages)

- SMT365G (23 pages)

- SMT364 (37 pages)

- SMT373 (15 pages)

- SMT370v3 (46 pages)

- SMT377 (22 pages)

- SMT381 2007 (31 pages)

- SMT381-VP (81 pages)

- SMT387 (42 pages)

- SMT391 (18 pages)

- SMT384 (47 pages)

- SMT390-VP (55 pages)