2 fpga reset scheme, Fpga reset scheme, Figure 8: cpld state machine – Sundance SMT368 User Manual

Page 14

The following table describes the settings for the jumper SW1 according to the various FPGA

configuration modes:

Configuration

SW1 Position

POS3 POS2 POS1

From CP_0

ON ON ON

From CP_3

OFF OFF OFF

From PROM

OFF OFF ON

Table 3: SW1 DIP switch for the configuration mode selection

At power-up the FPGA is not configured.

LED D1 (see Figure 7: Components placement - Top view) will be lit upon the

FPGA configuration.

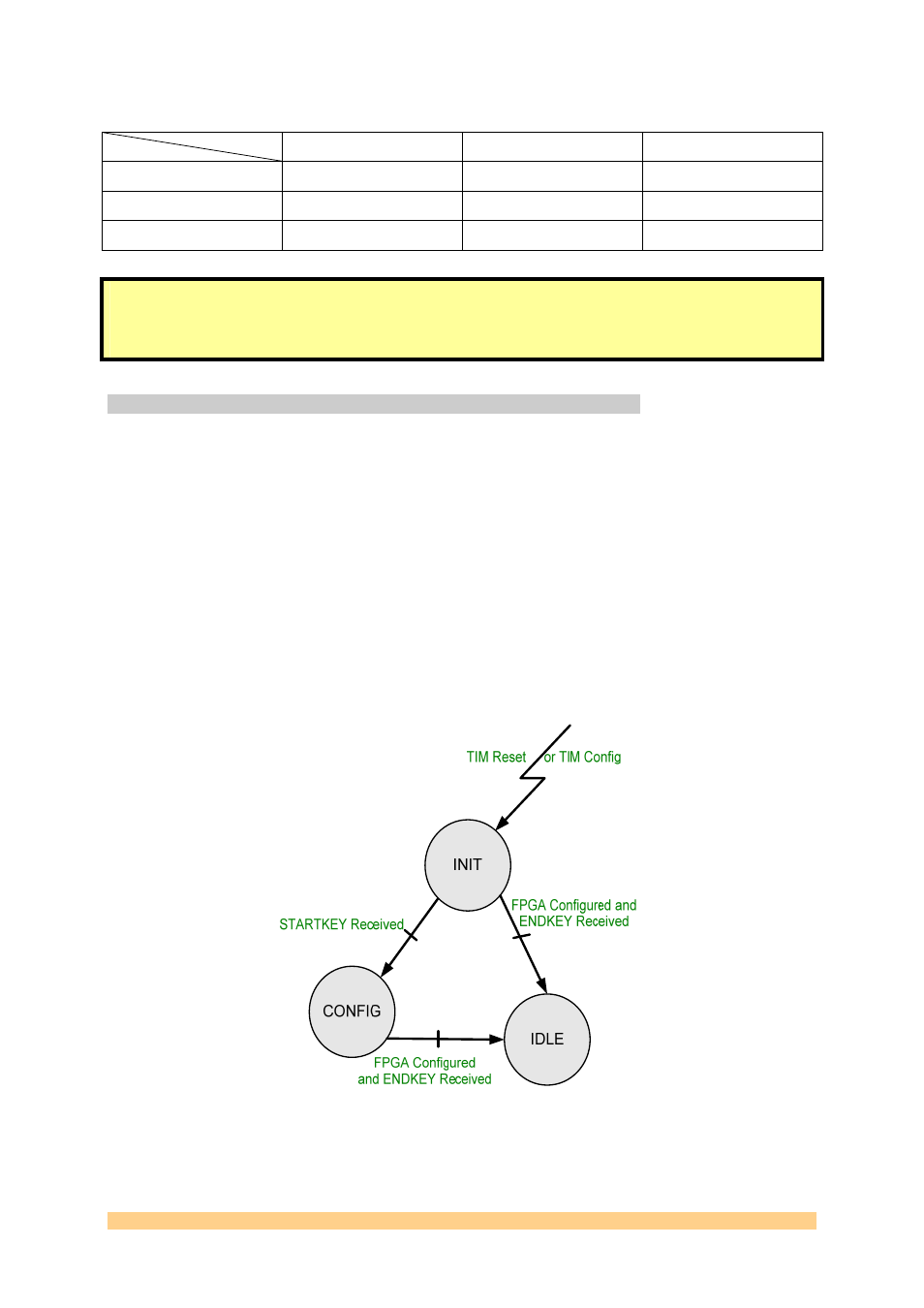

4.2.2 FPGA Reset Scheme

The CPLD is connected to the TIM global reset signal provided to the SMT368 via its primary

TIM connector (P1) pin 30.

The CPLD provides another signal called FPGAResetn that offers a better Reset control

over the FPGA.

At power-up or on reception of a low TIM global reset pulse, the CPLD drives the

FPGAResetn signal low and it keeps it low.

When the ENDKEY has been received, the CPLD drives the FPGAResetn high.

Sundance recommends you to use the FPGAResetn signal for the Global Reset signal of

your FPGA designs.

In this manner, you can control your FPGA design Reset activity and you will also avoid

possible conflicts on the ComPort_3 if your FPGA design implements it.

The Reset control is operated by the CPLD line FPGAResetn.

Figure 8: CPLD state machine

Note: The Reset level on the SMT368 is active low.

User Manual SMT368

Page 14 of 24

Last Edited: 31/12/2008 13:53:00