Sundance SMT300Q v.1.6 User Manual

Page 48

Page 48 of 61

SMT300Q SMT300Q User Guide V1.65

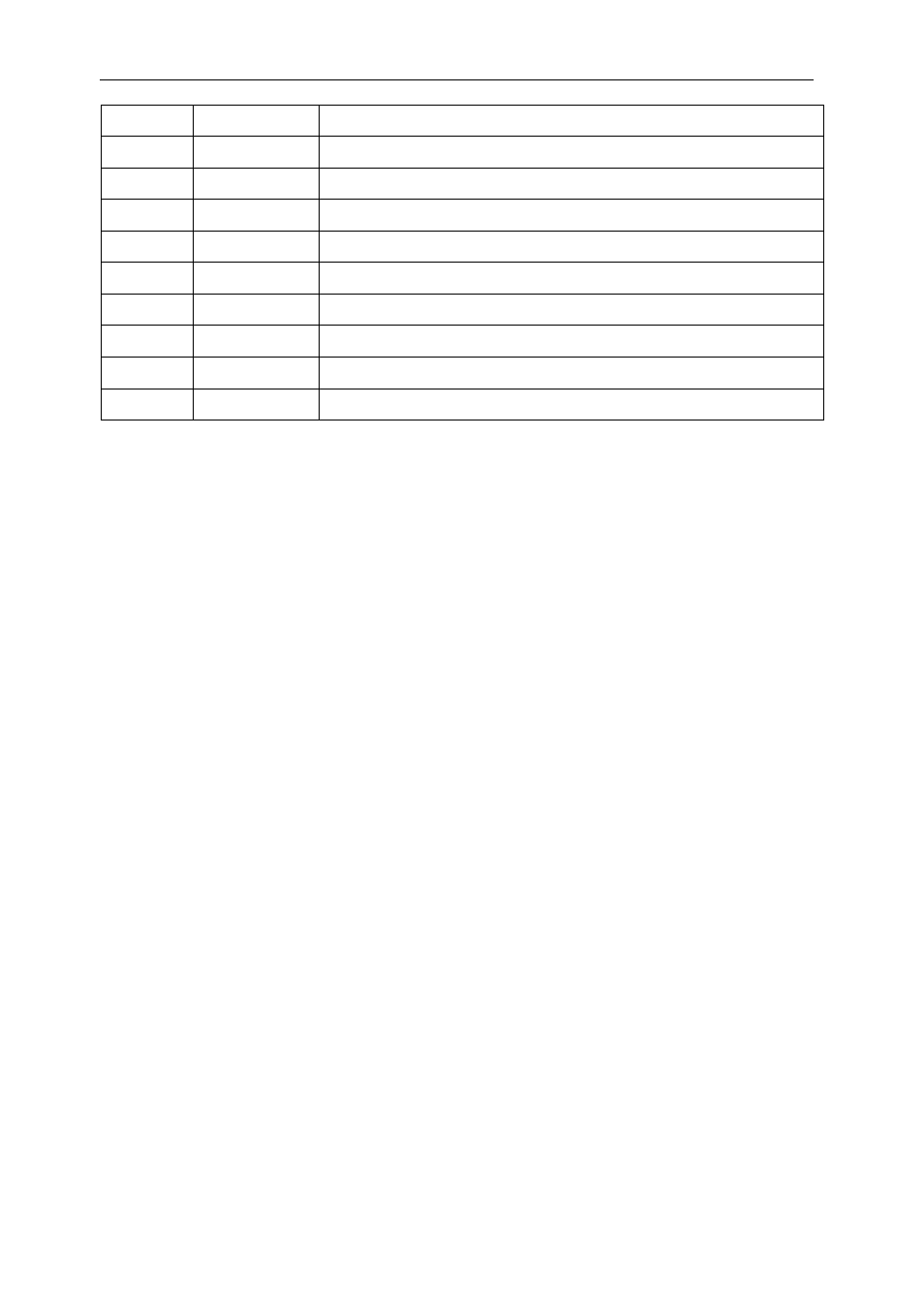

9 -

Reserved

8 -

Reserved

7 -

Reserved

6 -

Reserved

5 -

Reserved

4 -

Reserved

3 -

Reserved

2

IIOF2EN

PC to DSP TIMIIOF2 interrupt enable

1

IIOF1EN

PC to DSP TIMIIOF1 interrupt enable

0

IIOF0EN

PC to DSP TIMIIOF0 interrupt enable

Table 31 : INTREG Register

14.4 Example

The example below shows how the DSP can cause an interrupt on the PC by writing

to mailbox register 0.

The PC must first enable the interrupts, to do this the following register bits must be

altered, and an interrupt thread handler needs to be created.

CompactPCI Interrupt Configuration Register(Offset 0x4C, BAR0) – bit 31 must be

set.

Local Bus Interrupt Mask Register(Offset 0x77, BAR0) – bit 7 must be set.

Local Bus Mailbox WRITE/READ Interrupt Control Register(Offset Write 0xD4, BAR0

Read 0xD6, BAR0) – bit 0 of the write register (0xD4) must be set.*

An Interrupt service routine must be set up, in this the following register will need to

be cleared