9 pll – Sundance SMT300Q v.1.6 User Manual

Page 26

User Manual (QCF42); Version 3.0, 8/11/00; © Sundance Multiprocessor Technology Ltd. 1999

9 PLL

The PLL produces three programmable clocks that are available on the user-defined

pins of the TIM connectors (Bank2CLK pin 1 on J24, Bank3CLK pin 3 on J24,

Bank4CLK pin 8 on J23).

These clocks are programmable through registers PLLREG1 and PLLREG2 (BAR1

Offset 60

16

and 64

16

).

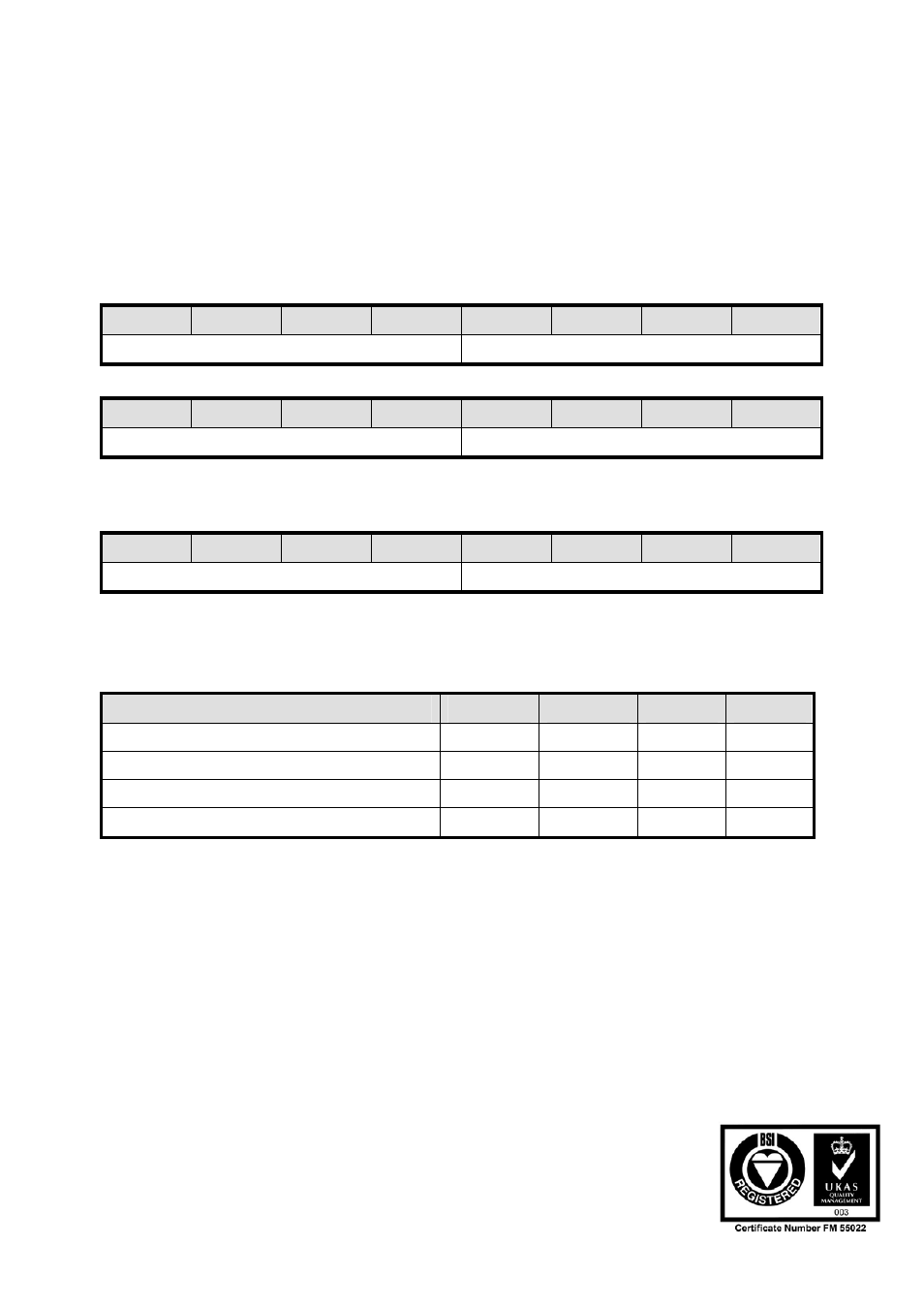

9.1 PLLREG1 (BAR1 Offset 60

16

)

D15

D14

D13

D12

D11

D10

D9

D8

Bank3CLK Frequency Select

Bank3CLK Phase Shift Select

D7

D6

D5

D4

D3

D2

D1

D0

Bank2CLK Frequency Select

Bank2CLK Phase Shift Select

Table 18 : PLLREG1 Register

9.2 PLLREG2 (BAR1 Offset 64

16

)

D7

D6

D5

D4

D3

D2

D1

D0

Bank4CLK Frequency Select

Bank4CLK Phase Shift Select

Table 19 : PLLREG2 Register

9.3 Frequency Select (Bank 2, 3 and 4)

Frequency (MHz)

MSB

LSB

66 / 1

0

1

0

1

66 / 3

0

1

1

1

66 / 8

1

1

0

1

66 / 12

1

1

1

1

Table 20 : PLL Frequency Select

Each clock output has a programmable phase shift in steps of t

u

.

Where t

u

= 1 / (F

NOM

* N)

F

NOM

= 66 MHz

N = 32

So t

u

= 473.5 ps