Sundance SMT300Q v.1.6 User Manual

Page 14

User Manual (QCF42); Version 3.0, 8/11/00; © Sundance Multiprocessor Technology Ltd. 1999

4 Host

Memory

Map

All address information is given in bytes :

4.1 CompactPCI

Bridge

Chip

Internal Register (BAR0)

Please see V363EPC Local Bus CompactPCI Bridge User Manual

(

http://www.quicklogic.com/home.asp?PageID=223&sMenuID=114#Docs

) for details

of internal registers.

Where required, registers from the V

3

datasheet have been included.

4.2 I/O Space Register Assignments (BAR1)

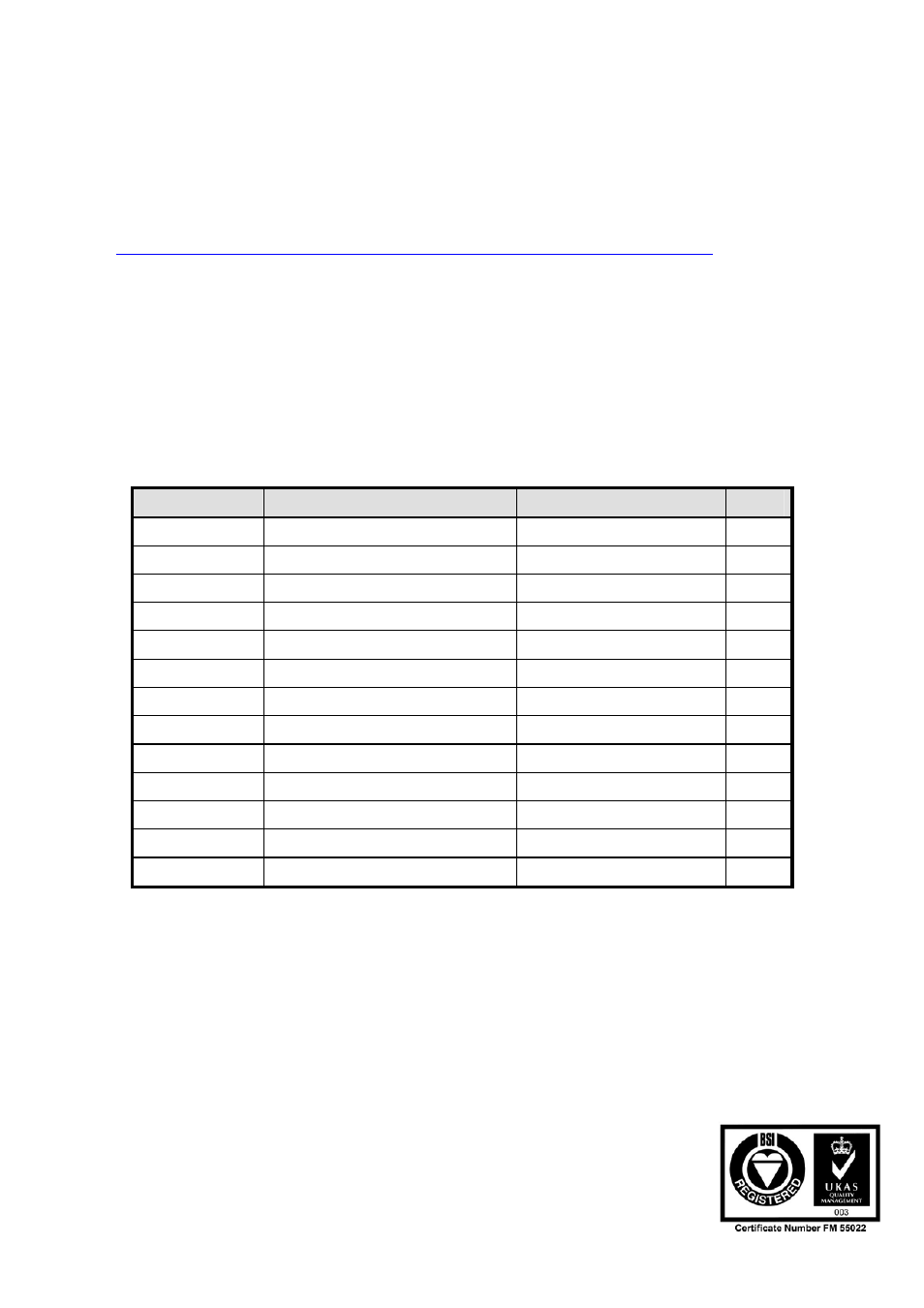

In target mode, a host device accesses the SMT300Q across the CompactPCI bus,

which gives access to the target mode registers. The operating system or BIOS will

normally allocate a base address for the target mode registers of each SMT300Q.

Access to each register within the SMT300Q is then made at offsets from this base

address as shown in the table below.

Offset (Hex)

Register(Write)

Register(Read)

Width

0x00 -

-

0x04 -

-

0x08 -

-

0x0C -

-

0x10 COMPORT_OUT COMPORT_IN

32

0x14 CONTROL

STATUS

32

0x18 INT_CONTROL

32

0x1C -

-

0x20 to 0x3F

COMPORT Configuration COMPORT

Configuration

0x24 COM_SWITCH COM_SWITCH

16

0x2C COM_SWITCH_EX

COM_SWITCH_EX

32

0x40

INTREG

INTREG

16

0x80 to 0xAF

TBC Write

TBC Read

16

Table 2 : I/O address space map