Measurement Computing Digital488 User Manual

Page 24

Section 2

Getting Started

2.8

2.3.3.4 Inhibit (Pin 44)

The Inhibit output is asserted while data on the selected I/O

port is being read into the I/O port buffer. This line is normally active

high but may be programmed active low by the Invert command (I1).

The Inhibit line can be programmed independent of any I/O

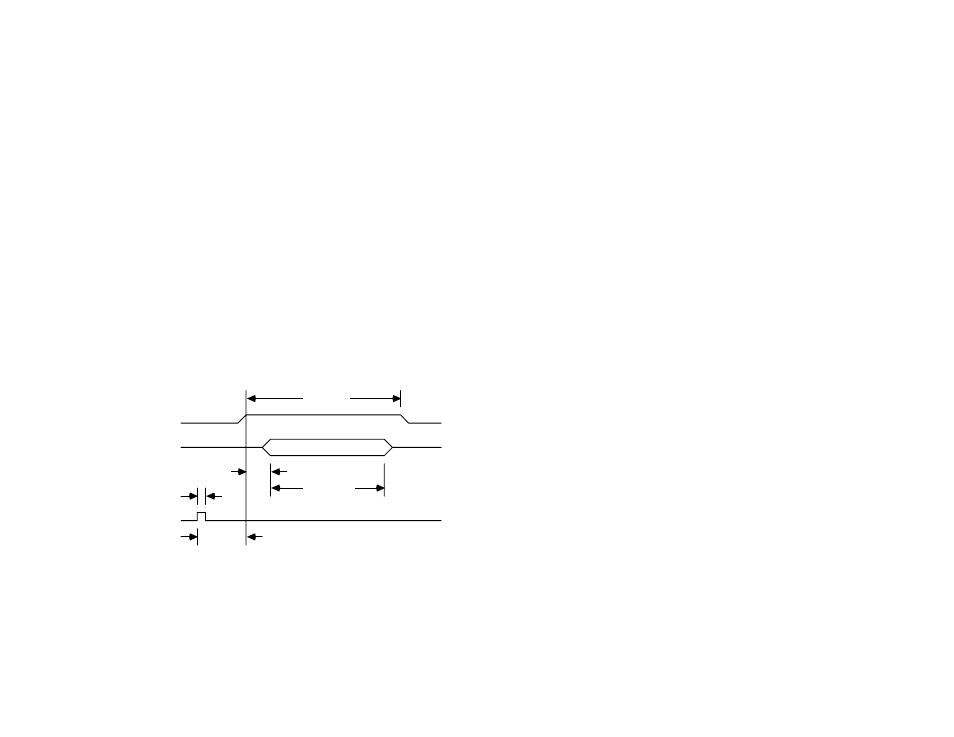

operations with the Inhibit command (Qn). Refer to the following

diagram for timing relationships.

The Inhibit line is asserted once for each data read operation

for all format [Fn] modes except high speed binary [F5]. In this mode,

it is asserted for the first data read after the Digital488 is addressed to

talk. On the last data byte transfer, the data is read again with Inhibit

asserted in anticipation of another data transfer. If Inhibit is used to

sequence external hardware, you should be aware that this line will

pulse N+1 times; where N is the number of total (5 byte) data

transfers.

Timing Diagram for EDR Input and Inhibit Output

1 µS min

50 µS typ

50 µS typ

50 µS max

10 µS min

DATA VALID

DATA

EDR

INHIBIT