Interrupt identification register – Measurement Computing COM232/8AT User Manual

Page 9

1000-0901, rev 1.1

March 1998

COM232/8AT User’s Guide

9

EDSSI MODEM Status Interrupt

− When set (logic 1), enables interrupt on Clear To Send, Data Set

Ready, Ring Indicator, and Data Carrier Detect.

ELSI Receiver Line Status Interrupt

− When set (logic 1), enables interrupt on Overrun, Parity,

Framing Errors, and Break Indication.

ETBEI Transmitter Holding Register Empty Interrupt

− When set (logic 1), enables interrupt on

Transmitter Register Empty.

ERBFI Received Data Available Interrupt

− When set (logic 1), enables interrupt on Received Data

Available. FIFO Mode

− When set (logic 1), enables interrupt when the receive FIFO trigger level is

reached. See the FIFO control register for trigger level selections.

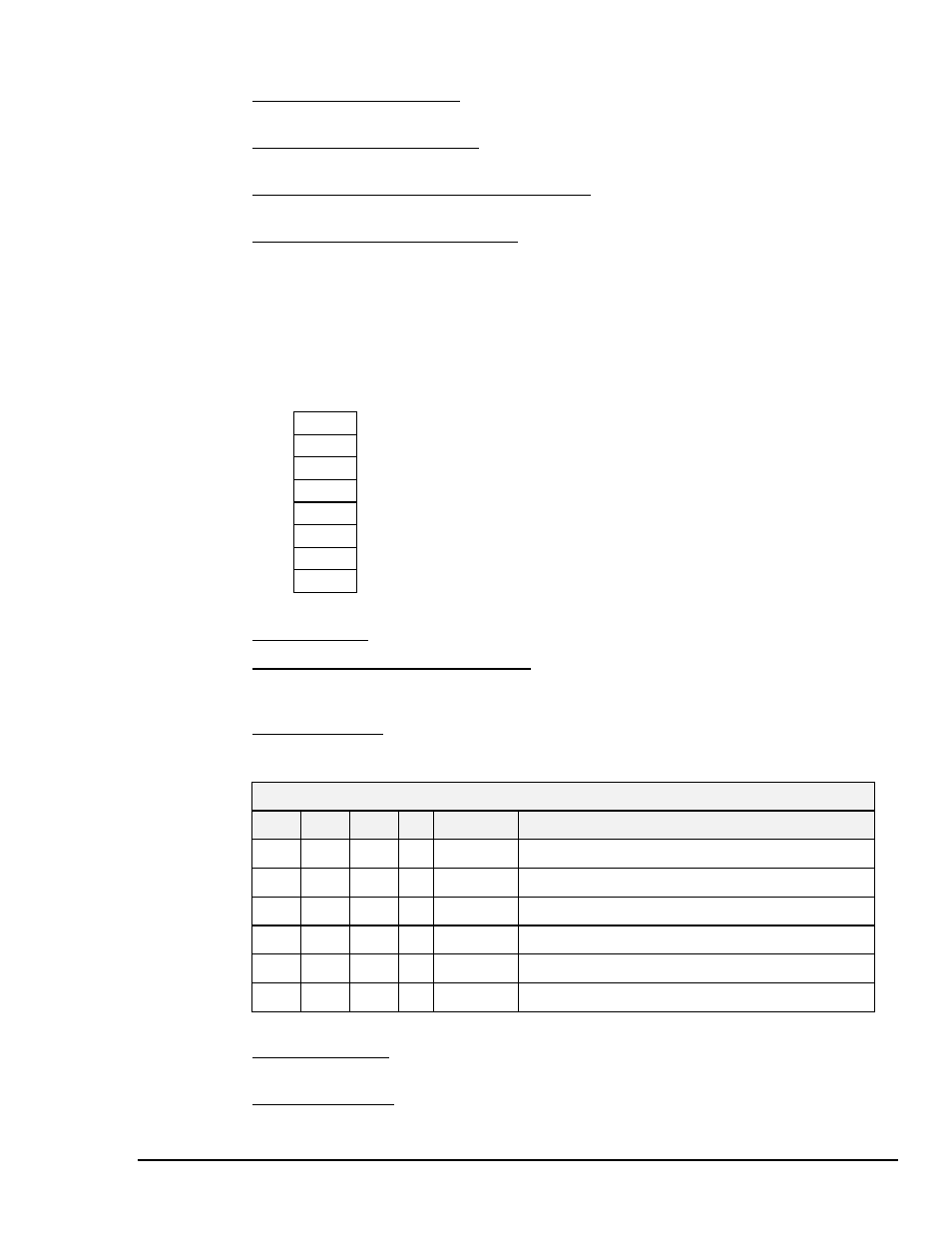

Interrupt Identification Register

Note: Do not confuse this register with the Interrupt ID Register.

The bit definitions for the Interrupt Identification Register are as follows:

Interrupt Identification Register Definitions

D7

FFE

FIFO Enable (FIFO only)

D6

0

D5

0

D4

0

D3

IID2

IID0, IID1 & IID2 are Interrupt Identifications

D2

IID1

D1

IID0

D0

IP

Interrupt Pending

FFE FIFO Enable

− When logic 1, indicates FIFO mode is enabled.

IID0, IID1, & IID2 Interrupt Identifications

− Indicates highest priority interrupt pending, if any. See

IP (Interrupt Pending) as well as the following table regarding bit definitions. Note that IID2 is always

logic 0 in the 16550 character mode.

IP Interrupt Pending

− When logic 0, indicates that an interrupt is pending and that the contents of the

interrupt identification register may be used to determine the source of the interrupt. See IID0, IID1,

IID2, as well as the following table.

Bit Definitions for Interrupt Identifications

IID2

IID1

IID0

IP

Priority

Interrupt Type

x

x

x

1

N/A

None.

0

1

1

0

Highest

Receiver Line Status

0

1

0

0

Second

Received Data Ready

1

1

0

0

Second

Character Timeout (FIFO Mode only)

0

0

1

0

Third

Transmitting Holding Register Empty

0

0

0

0

Fourth

MODEM Status

Receiver Line Status

− Indicates overrun, parity, framing errors or break interrupts. The interrupt is

cleared by reading the line status register.

Received Data Ready

− Indicates receiver data available. The interrupt is cleared by reading the

receiver buffer register. FIFO Mode

− Indicates the receiver FIFO trigger level has been reached.

The interrupt is reset when the FIFO drops below the trigger level.