Fifo control register – Measurement Computing COM232/8AT User Manual

Page 10

10 COM232/8AT User’s Guide

March 1998

1000-0901, rev 1.1

Character Timeout (FIFO Mode only)

− Indicates no characters have been removed from, or input to

the receiver FIFO for the last four character times and that there is at least one character in the FIFO

during this time. The interrupt is cleared by reading the receiver FIFO.

Transmitter Holding Register Empty

− Indicates that the transmitter holding register is empty. The

interrupt is cleared by reading the interrupt identification register, or by writing to the transmitter

holding register.

MODEM Status

− Indicates Clear To Send, Data Set Ready, Ring Indicator, or Data Carrier Detect

have changed state. The interrupt is cleared when the MODEM Status Register is read.

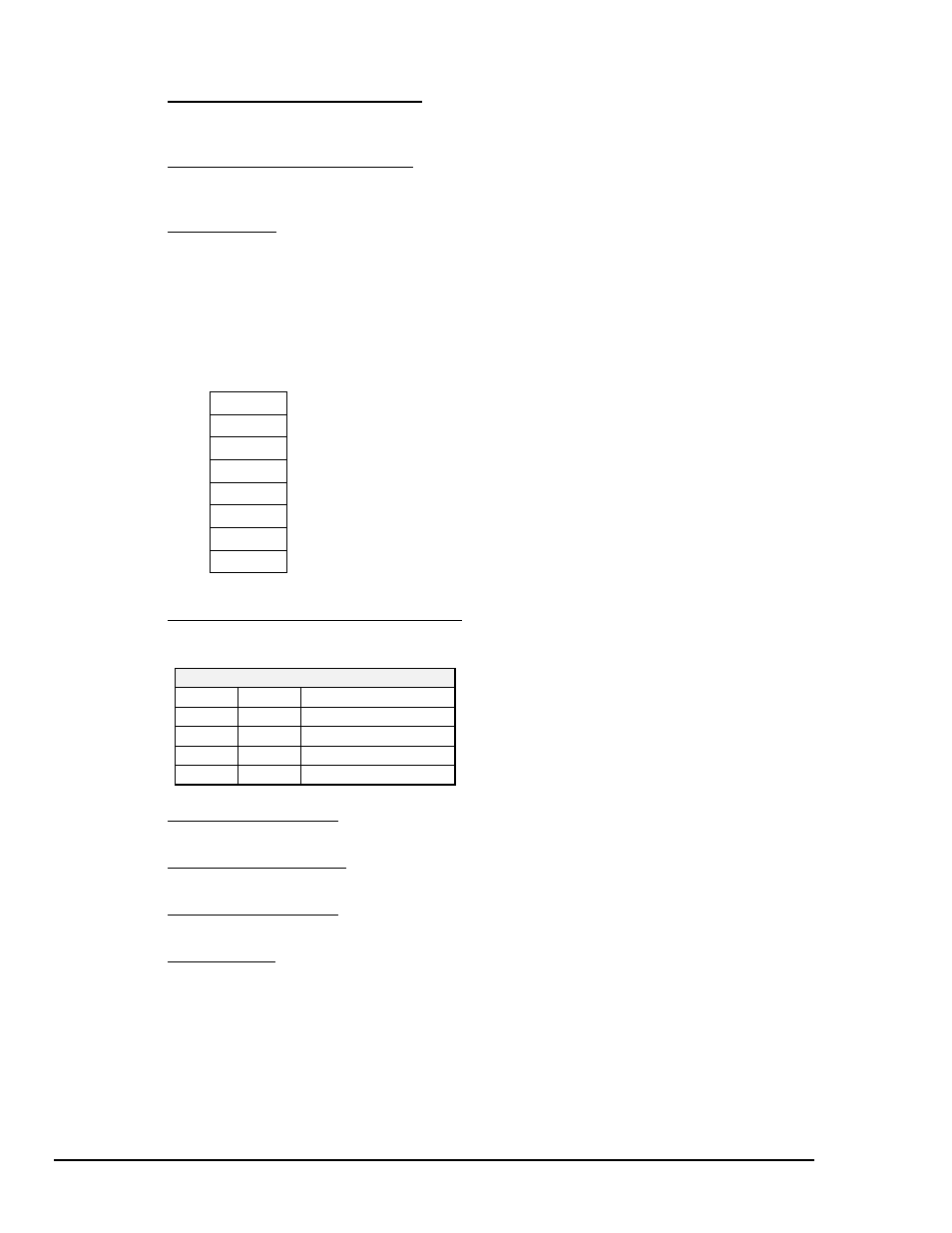

FIFO Control Register

The bit definitions for the FIFO Control Register are as follows:

FIFO Control Register Definitions

D7

RXT1

RXT0 and RXT1 are Receiver Trigger Levels

D6

RXT0

D5

x

D4

x

D3

DMAM

DMA Mode Select

D2

XRST

Transmit FIFO Reset

D1

RRST

Receive FIFO Reset

D0

FE

FIFO Enable

RXT0 & RXT1 Receiver FIFO Trigger Levels

− Determines the trigger level for the FIFO interrupt as

indicated in the following table.

FIFO Trigger Levels

RXT1

RXT0

Trigger Level

(bytes)

0

0

1

0

0

4

1

0

8

1

1

14

DMAM DMA Mode Select

− Selects the mode of the RxRDY and TxRDY outputs. Note that the

DMA mode is not supported on the RW-100T.

XRST Transmit FIFO Reset

− When set (logic 1), all bytes in the transmitter FIFO are cleared and the

counter is reset. The shift register is not cleared. XRST is self-clearing.

RRST Receive FIFO Reset

− When set (logic 1), all bytes in receiver FIFO are cleared and the counter

is reset. The shift register is not cleared. RRST is self-clearing.

FE FIFO Enable

− When set (logic 1), enables transmitter and receiver FIFOs. When cleared

(logic 0), all bytes in both FIFOs are cleared. This bit must be set when other bits in the FIFO control

register are written to, otherwise the bits will be ignored.