Modem control register – Measurement Computing COM232/8AT User Manual

Page 12

12 COM232/8AT User’s Guide

March 1998

1000-0901, rev 1.1

MODEM Control Register

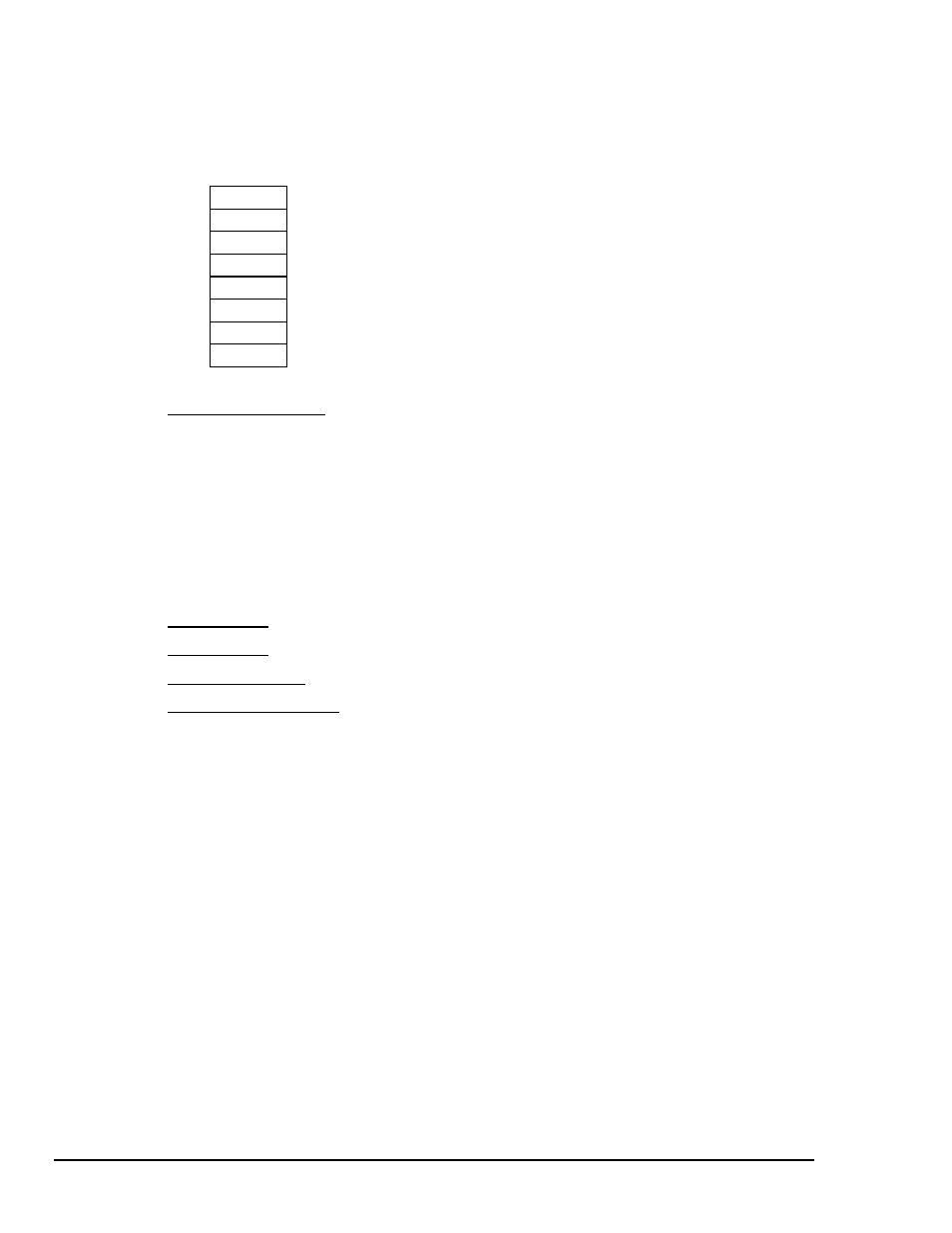

The bit definitions for the MODEM Control Register are as follows:

MODEM Control Register Definitions

D7

0

D6

0

D5

0

D4

LOOP

Loopback Enable

D3

OUT2

Output 2

D2

OUT1

Output 1

D1

RTS

Request to Send

D0

DTR

Data Terminal Ready

LOOP Loopback Enable

− When set (logic 1), the transmitter shift register is connected directly to the

receiver shift register. The MODEM control inputs are internally connected to the MODEM control

outputs and the outputs are force to the inactive state. For this reason all transmitted characters are

immediately received to verify the transmit and receive data paths. Note that the transmitter and

receiver interrupts still undergo normal operation. MODEM control interrupts are available, but are

now controlled through the MODEM Control Register.

Note:

Bits OUT2, OUT1, RTS, and DTR (described below) perform identical functions on their

respective outputs. In each case, when the bit is set (logic 1) in the register, the associated

output is forced to logic 0. When cleared (logic 0), the associated output is forced to logic 1.

OUT2 Output 2

− Controls the OUT2 output [pin 31] as described in the above note.

OUT1 Output 1

− Controls the OUT1 output [pin 34] as described in the above note.

RTS Request To Send

− Controls the RTS output [pin 32] as described in the above note.

DTR Data Terminal Ready

− Controls the DTR output [pin 33] as described in the above note.