Digi NS9210 User Manual

Page 27

. . . . .

www.digiembedded.com

27

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

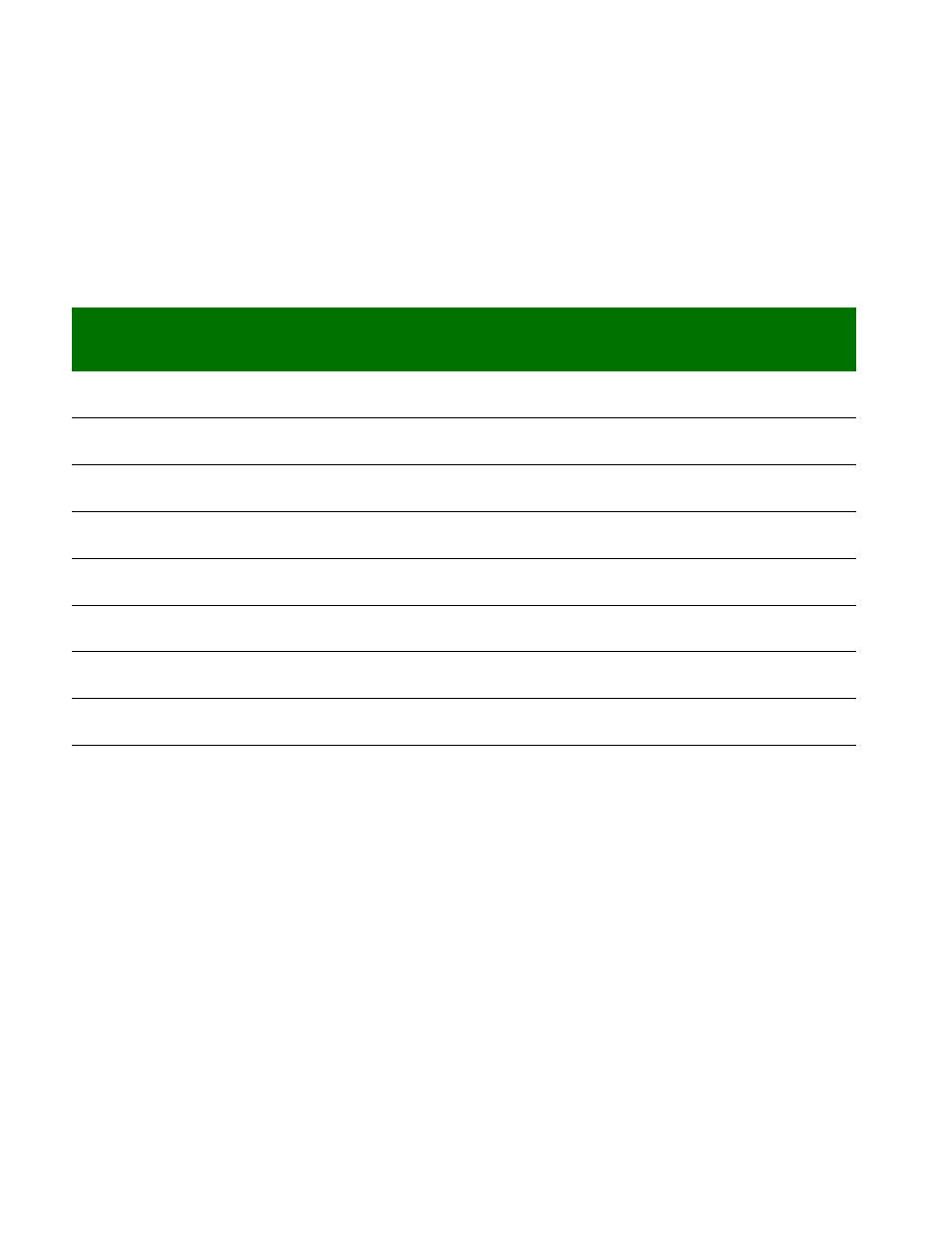

C h i p s e l e c t s

The module has eight chip selects: four for dynamic memory and four for static

memory. Each chip select has a 256MB range.

Chip select

memory map

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

S D R A M b a n k s

The module provides connection to 1 SDRAM chip, connected to CS1# (SDM_CS0#).

The other SDRAM chip selects are not used.

The standard module has one of these SDRAM onboard: 1Mx16x4-banks. A13 is the

highest address connected. BA0 and BA1 are connected to A21 and A22,

respectively.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

M u l t i p l e x e d G P I O p i n s

The 64 GPIOs pins available on the module connector are multiplexed with other

functions like:

Name

CPU

Sig.

name

Pin

Address range

Size

[Mb]

Usage

Comments

SDM_CS0#

CS1#

D6

0x00000000–

0x0FFFFFFF

256

SDRAM bank 0

First bank on module

SDM_CS1#

CS3#

B5

0x10000000–

0x1FFFFFFF

256

not used

SDM_CS2#

CS5#

A4

0x20000000–

0x2FFFFFFF

256

not used

SDM_CS3#

CS7#

B4

0x30000000–

0x3FFFFFFF

256

not used

EXT_CS0#

CS0#

C6

0x40000000–

0x4FFFFFFF

256

external, CS0#

INT_CS1#

CS2#

B6

0x50000000–

0x5FFFFFFFF

256

NOR-Flash

Program memory on

module

EXT_CS2#

CS4#

C5

0x60000000–

0x6FFFFFFFF

256

external, CS2#

INT_CS3#

CS6#

A3

0x70000000–

0x7FFFFFFF

256

internal, CS3#

Reserved for internal usage