3 ebus/mii bridge port (logical port 3), Ebus/mii bridge port (logical port 3), Table 27: mapping of ebus bridge signals – BECKHOFF ET1200 User Manual

Page 32: Table 28: mapping of mii bridge signals

Pin Description

III-22

Slave Controller

– ET1200 Hardware Description

3.8.3

EBUS/MII bridge port (Logical port 3)

The bridge port is an additional port with logical number 3, it is configured via SII EEPROM, thus it is

not available directly after power-on. The bridge port becomes available once the EEPROM is loaded

successfully. The loop at this port is initially closed and has to be opened by the master explicitly. The

bridge port may be either EBUS or MII. The MII bridge port is only available in chip mode 00.

The polarity of PERR(3) and LINKACT(3) is active high.

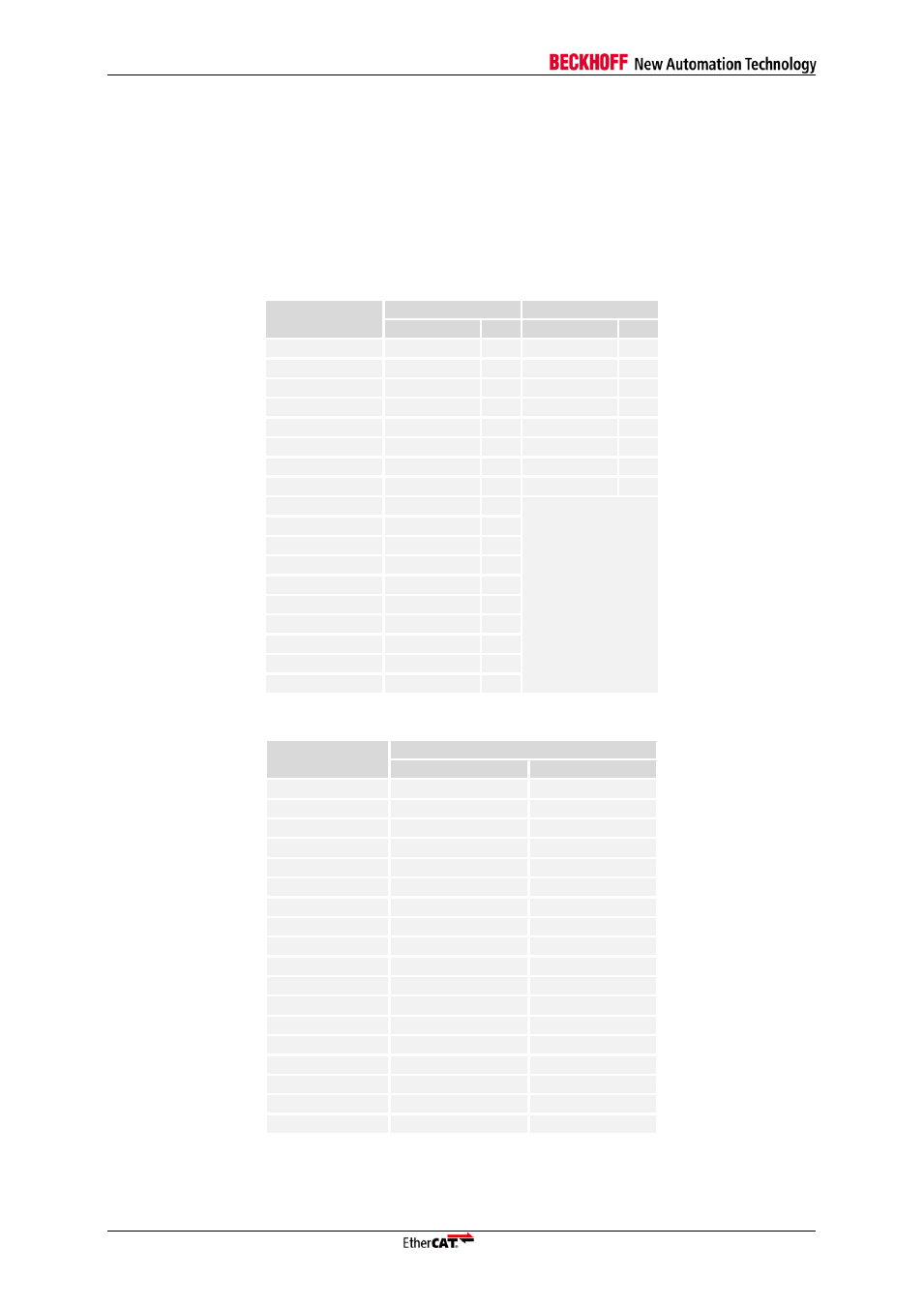

Table 27: Mapping of EBUS Bridge signals

PDI Signal

MODE[1:0]=00

MODE[1:0]=10/11

Signal

Dir.

Signal

Dir.

PDI[0]

EBUS(3)_TX+

LO+

EBUS(3)_TX+

LO+

PDI[1]

EBUS(3)_TX-

LO-

EBUS(3)_TX-

LO-

PDI[2]

EBUS(3)_RX+

LI+

EBUS(3)_RX+

LI+

PDI[3]

EBUS(3)_RX-

LI-

EBUS(3)_RX-

LI-

PDI[4]

PERR(3)

O

PERR(3)

O

PDI[5]

LINKACT(3)

O

LINKACT(3)

O

PDI[6]/CLK25OUT

GPO[0]

O

GPO[0]

O

PDI[7]/CPU_CLK

GPO[1]

O

GPO[1]

O

PDI[8]

GPO[2]

O

MII

PDI[9]

GPO[3]

O

PDI[10]

GPO[4]

O

PDI[11]

GPO[5]

O

PDI[12]

GPO[6]

O

PDI[13]

GPO[7]

O

PDI[14]

GPO[8]

O

PDI[15]

GPO[9]

O

PDI[16]

GPO[10]

O

PDI[17]

GPO[11]

O

Table 28: Mapping of MII Bridge signals

PDI Signal

MODE[1:0]=00

Signal

Dir.

PDI[0]

TX_ENA(3)

O

PDI[1]

MI_CLK

O

PDI[2]

RX_ERR(3)

I

PDI[3]

LINK_MII(3)

I

PDI[4]

PERR(3)

O

PDI[5]

LINKACT(3)

O

PDI[6]/CLK25OUT

CLK25OUT

O

PDI[7]/CPU_CLK

GPO[1]

O

PDI[8]

TX_D(3)[0]

O

PDI[9]

TX_D(3)[1]

O

PDI[10]

TX_D(3)[2]

O

PDI[11]

TX_D(3)[3]

O

PDI[12]

RX_CLK(3)

I

PDI[13]

RX_DV(3)

I

PDI[14]

RX_D(3)[0]

I

PDI[15]

RX_D(3)[1]

I

PDI[16]

RX_D(3)[2]

I

PDI[17]

RX_D(3)[3]

I