1 ethercat state machine registers, 1 al control and al status register, 2 device emulation – BECKHOFF EtherCAT Technology Section I User Manual

Page 91: 3 error indication and al status code register, Ethercat state machine registers, Al control and al status register, Device emulation, Error indication and al status code register, Table 35: registers for the ethercat state machine, Table 36: al control and al status register values

EtherCAT State Machine

Slave Controller

– Technology

I-71

10.1 EtherCAT State Machine Registers

The state machine is controlled and monitored via registers within the ESC. The master requests state

changes by writing to the AL Control register. The slave indicates its state in the AL Status register

and puts error codes into the AL Status Code register.

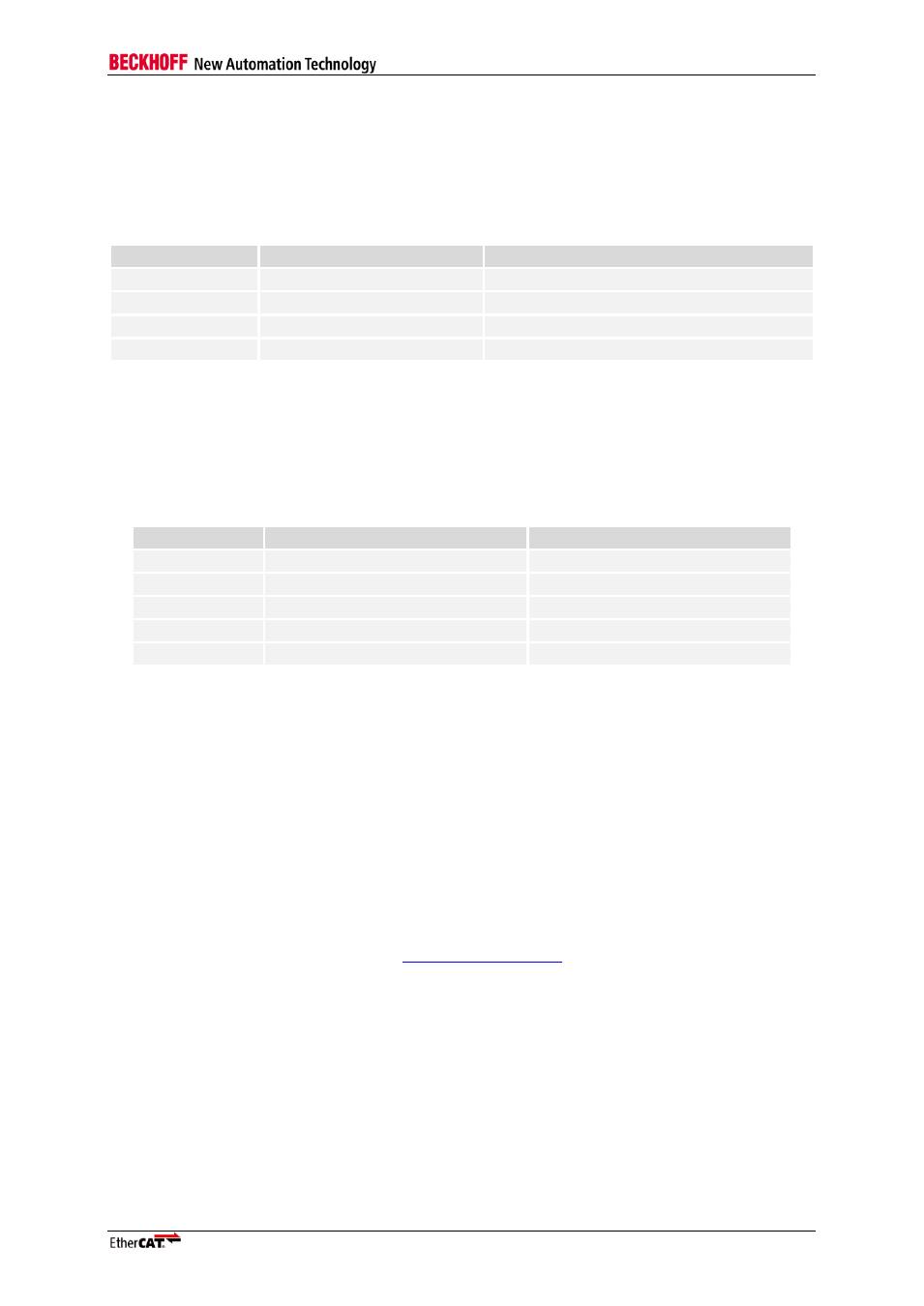

Table 35: Registers for the EtherCAT State Machine

Register Address

Name

Description

0x0120:0x0121

AL Control

Requested state by the master

0x0130:0x0131

AL Status

AL Status of the slave application

0x0134:0x0135

AL Status Code

Error codes from the slave application

0x0141[0]

ESC Configuration

Device emulation configuration

NOTE: The PDI Control register is set via SII EEPROM/IP Core configuration, other registers might not be

available in specific ESCs. Refer to Section II and Section III for details.

10.1.1 AL Control and AL Status Register

Writing the AL Control register (0x0120:0x0121) initiates a state transition of the device state machine.

The AL Status register (0x0130:0x0131) reflects the current state of the slave.

Table 36: AL Control and AL Status Register Values

Register [3:0]

AL Control Register 0x0120

AL Status Register 0x0130

1

Request Init state

Init state

3

Request Bootstrap state (optional)

Bootstrap state (optional)

2

Request Pre-Operational state

Pre-Operational state

4

Request SAFE-Operational state

SAFE-Operational state

8

Request Operational state

Operational state

10.1.2 Device Emulation

Simple devices (without µController) have the device emulation enabled (0x0141[0]=1). The AL

Control register is directly copied into the AL Status register by the ESC. The master should not set

the Error Indication Acknowledge bit for such slaves at all, because setting this bit would result in

setting the Error Indication bit

– although no error occurred.

10.1.3 Error Indication and AL Status Code Register

The slave indicates errors during a state transition by setting the Error Indication flag (0x0130[4]=1)

and writing an error description into the AL Status Code register (0x0134:0x0135). The master

acknowledges the Error Indication flag of the slave by setting the Error Indication Acknowledge flag

(0x0120[4]).

For more information on defined AL Status Codes, refer to the EtherCAT Knowledge Base available at

the EtherCAT Technology Group website

uidelines and Protocol

Enhancements).