Document history – BECKHOFF EtherCAT Technology Section I User Manual

Page 3

DOCUMENT HISTORY

Slave Controller

– Technology

I-III

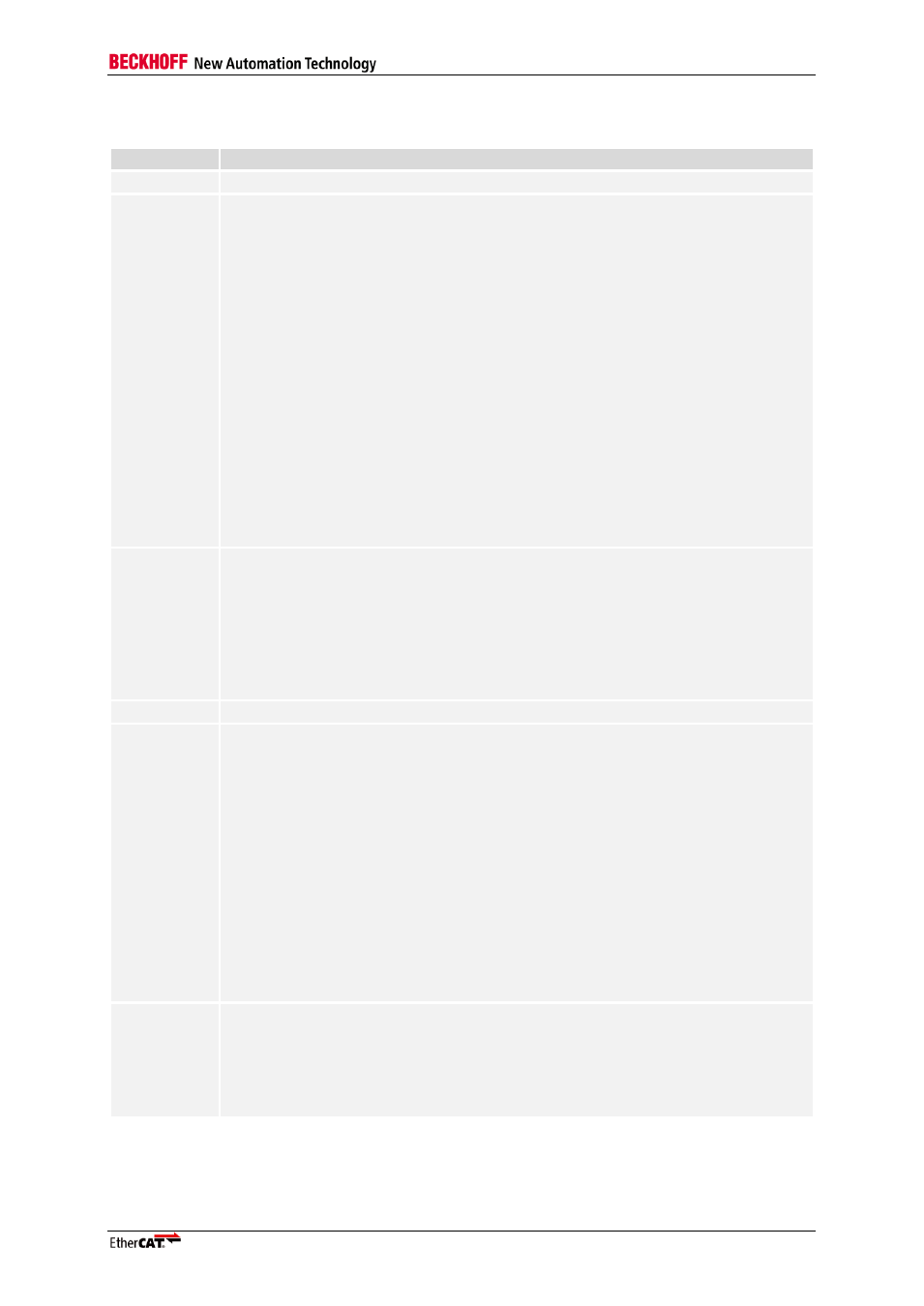

DOCUMENT HISTORY

Version

Comment

1.0

Initial release

1.1

Chapter Interrupts

– AL Event Request: corrected AL Event Mask register

address to 0x0204:0x0207

EtherCAT Datagram: Circulating Frame bit has position 14 (not 13)

PHY addressing configuration changed

Loop control: a port using Auto close mode is automatically opened if a valid

Ethernet frame is received at this port

EEPROM read/write/reload example: steps 1 and 2 swapped

EEPROM: Configured Station Alias (0x0012:0x0013) is only taken over at first

EEPROM load after power-on or reset

SyncManager: Watchdog trigger and interrupt generation in mailbox mode with

single byte buffers requires alternating write and read accesses for some ESCs,

thus buffered mode is required for Digital I/O watchdog trigger generation

National Semiconductor DP83849I Ethernet PHY deprecated because of large

link loss reaction time and delay

Added distinction between permanent ports and Bridge port (frame processing)

Added PDI chapter

PDI and DC Sync/Latch signals are high impedance until the SII EEPROM is

successfully loaded

Editorial changes

1.2

PHY address configuration revised. Refer to Section III for ESC supported

configurations

Added Ethernet Link detection chapter

Added MI Link Detection and Configuration, link detection descriptions updated

Added EEPROM Emulation for EtherCAT IP Core

Added General Purpose Input chapter

Corrected minimum datagram sizes in EtherCAT header figure

Editorial changes

1.2.1

Chapter 5.1.1: incompatible PHYs in footnote 1 deleted

1.3

Added advisory for unused MII/RMII/EBUS ports

Ethernet PHY requirements revised: e.g., configuration by strapping options,

recommendations enhanced. Footnote about compatible PHYs removed,

information has moved to the

EtherCAT Slave Controller application note “PHY

Selection Guide”.

Frame Error detection chapter enhanced

FIFO size reduction chapter enhanced

EBUS enhanced link detection chapter enhanced

Ethernet PHY link loss reaction time must be faster than 15 µs, otherwise use

Enhanced link detection

Enhanced link detection description corrected. Enhanced link detection does

not remain active if it is disabled by EEPROM and EBUS handshake frames are

received

ARMW/FRWM commands increase the working counter by 1

Editorial changes

1.4

Update to EtherCAT IP Core Release 2.1.0/2.01a

Added restriction to enhanced link configuration: RX_ER has to be asserted

outside of frames (IEEE802 optional feature)

ESC power-on sequence for IP Core corrected

Removed footnote on t

Diff

figures, refer to Section III for actual figures

Editorial changes