3 syncsignal generation, Syncsignal generation, Table 32: syncsignal generation mode selection – BECKHOFF EtherCAT Technology Section I User Manual

Page 81: Figure 30: syncsignal generation modes

Distributed Clocks

Slave Controller

– Technology

I-61

9.2.3

SyncSignal Generation

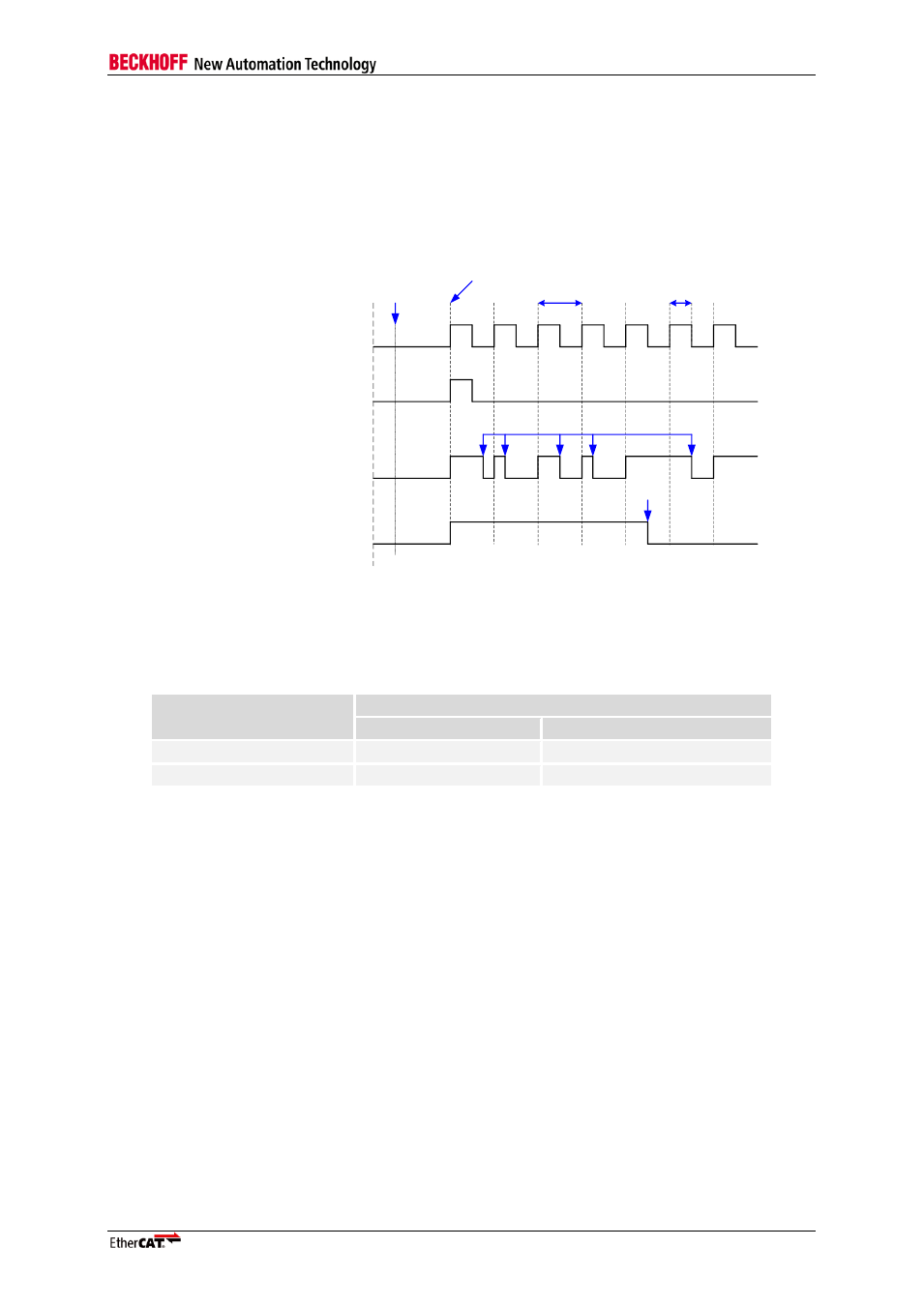

The DC Cyclic Unit / Sync Unit supports the generation of a base SyncSignal SYNC0 and a

dependent SyncSignal SYNC1. The SyncSignals can both be used internally and externally of the

ESC. SyncSignals can be generated at a specific System Time. Four operation modes are supported:

cyclic generation, single shot, cyclic acknowledge, and single shot acknowledge mode. The

acknowledged modes are typically used for interrupt generation. The interrupts have to be

acknowledged by a µController.

SYNC0

Acknowlege

SYNC0

SYNC0

Single shot

Cyclic generation

Cyclic Acknowledge mode

Activation

SYNC0 Cycle Time

Acknowlege

SYNC0

Single shot Acknowledge mode

Start Time

Pulse Length of

SyncSignals

Figure 30: SyncSignal Generation Modes

The SyncSignal operation mode is selected by the configuration of the Pulse Length and the SYNC0

Cycle Time, according to the following table:

Table 32: SyncSignal Generation Mode Selection

Pulse Length of SYNC

Signals (0x0982:0x0983)

SYNC0 Cycle Time (0x09A0:0x09A3)

> 0

= 0

> 0

Cyclic Generation

Single Shot

= 0

Cyclic Acknowledge

Single Shot Acknowledge

The cycle time of the SYNC0 signal is configured in the SYNC0 Cycle Time register (0x09A0:0x09A3),

the start time is set in the Start Time Cyclic Operation register (0x0990:0x0997). After the Sync Unit is

activated and the output of the SYNC0/1 signals is enabled (DC Activation register 0x0981), the Sync

Unit waits until the start time is reached and generates the first SYNC0 pulse.

Some ESCs support additional activation options like auto-activation when the Start Time is written, or

64 bit extension if only 32 bit of the Start Time is written. Other options are to detect invalid Start

Times and provide debug output of SyncSignals.

Internally, the SyncSignals are generated with an update rate of 100 MHz (10 ns update cycle). The

jitter of the internal SyncSignal generation in comparison to the System Time is 12 ns.