Ez80f91 module, Figure 23, Connector 2 connector 1 – Zilog EZ80F91 User Manual

Page 67

UM014220-0508

Schematic

Diagrams

eZ80F91 Development Kit

User Manual

62

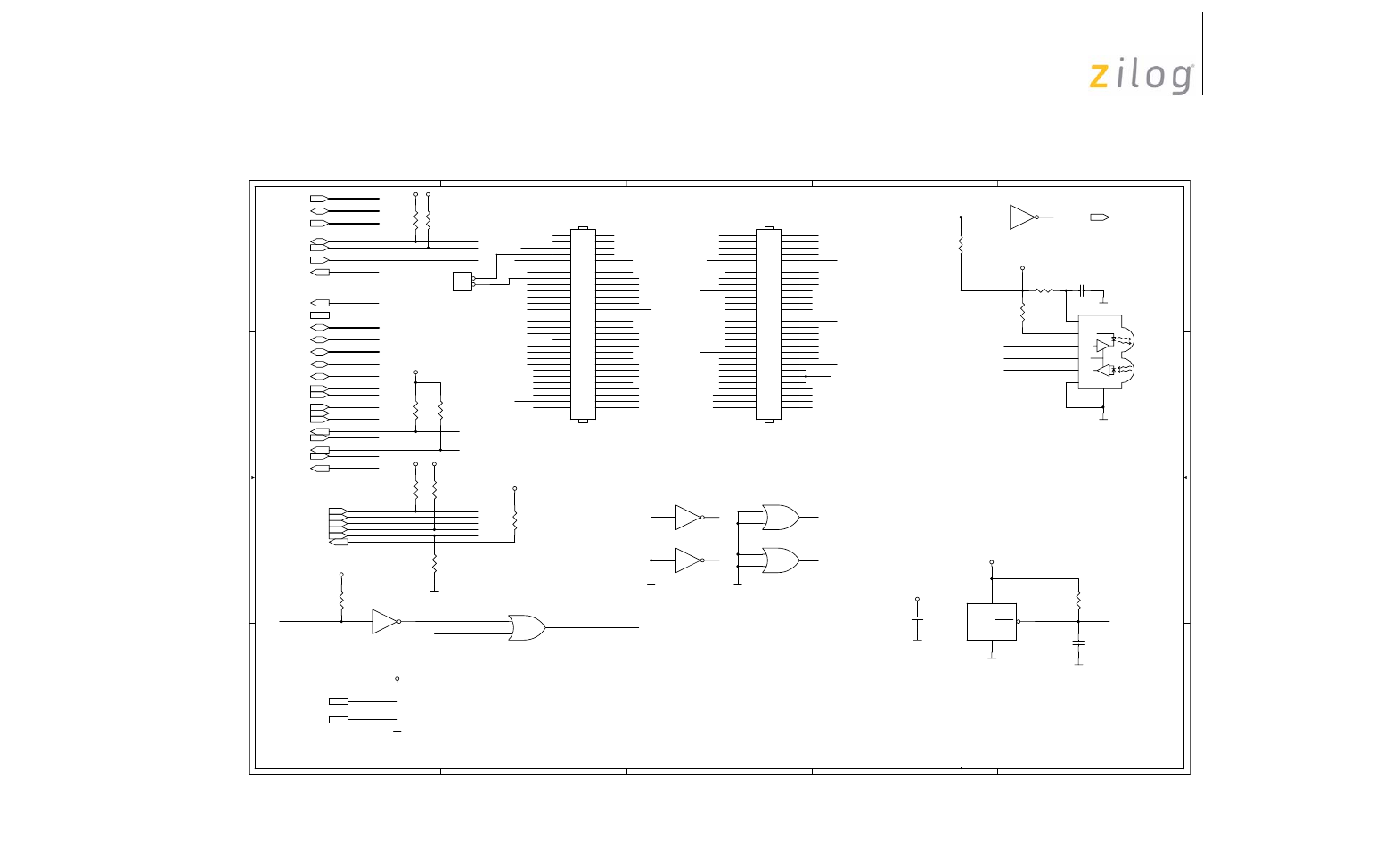

eZ80F91 Module

through

displays the layout of the eZ80F91 Module. Ethernet circuiting devices are not loaded on the eZ80F91 Module.

However, these devices appear in the following schematics for reference purposes.

Figure 23. eZ80F91 Module Schematic Diagram, #1 of 3—Connectors and Miscellaneous

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

connector 2

connector 1

=

(MMA 0204)

open-drain

alternative:

Maxim

MAX6802UR29D3

Memory

WR_EN

96C0879-001

B

eZ80F91 Ethernet Module.

ZiLOG, Inc.

532 Race Street. San Jose,CA 95126. 408.558.8500

B

1

3

Thursday, November 06, 2003

Title

Size

Document Number

Rev

Date:

Sheet

of

D3

PD1

-RD

-BUSREQ

-BUSREQ

GND

TDO

D[0..7]

A8

-CS0

-DIS_FLASH

-RESET

A22

-WR

RTC_VDD

-BUSACK

A[0..23]

PD3

-WR

-HALT_SLP

-MREQ

A19

A13

-FLASHWE

A10

D5

-RESET

-WAIT

-WAIT

TDO

GND

PD5

PB1

-NMI

-IOREQ

A5

PD6

-MREQ

D7

-CS[0..3]

A11

-CS2

-FLASHWE

PB[0..7]

A15

A18

A2

PB3

IICSDA

PC2

-INSTRD

PC6

GND

-BUSACK

PC[0..7]

TMS

D1

A4

TCK

PB5

-HALT_SLP

PC4

IICSCL

TCK

PC0

IICSCL

A21

PD[0..7]

GND

TRIGOUT

TDI

A6

PB7

-CS3

RTC_VDD

IICSDA

CLK_OUT

EZ80CLK

IICSDA

IICSCL

-DIS_IRDA

IR_SD

PD2

DISABLE_IRDA

IRDA_SD

PD0

IRDA_SD

PD1

A17

D2

A16

A1

-BUSREQ

GND

D6

A9

-CS1

A23

-IOREQ

A0

A7

GND

D4

A12

-DIS_FLASH

D0

-INSTRD

-RD

A20

A14

PD7

PD2

PB4

-DIS_IRDA

PD4

TMS

PC5

PB6

EZ80CLK

PD0

PC7

-NMI

PB0

GND

TRIGOUT

-WAIT

PC3

PB2

PC1

GND

TDI

GND

GND

GND

PA7

PA5

PA3

PA1

PA6

PA4

PA2

PA0

-TRSTN

-F91_WE

-F91_WP

-RESET

PA[0..7]

A3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

-TRSTN

-F91_WE

GND

GND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

GND

GND

VCC

R3

68R

R37

10K

C1

330nF

R12

10K

R6

2.2K

R4

2R7

R2

4.7K

C2

0.1uF

U1C

74LCX04

TSSOP14

5

6

C3

0.01uF

R20

10K

U1B

74LCX04

TSSOP14

3

4

U1A

74LCX04

TSSOP14

1

2

R5

2.2K

R7

10K

R8

10K

R1

4.7K

U4A

74LCX32

TSSOP14

1

2

3

R9

4.7K

U3

MAX6328UR29

SOT-23-L3

2

1

3

RESET

GND

V

DD

JP2

HEADER 30x2/SM

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

U4D

74LCX32

TSSOP14

12

13

11

U2

ZHX1810

2

4

3

1

5

6

0

TXD

SD

RXD

LEDA

VCC

GND

T

U1F

74LCX04

TSSOP14

13

12

R10

10K

JP1

HEADER 30x2/SM

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

JP3

1

2

U4B

74LCX32

TSSOP14

4

5

6

-BUSACK

TDO

PB[0..7]

-WR

-NMI

-FLASHWE

CLK_OUT

-HALT_SLP

-MREQ

IICSDA

-BUSREQ

-RD

D[0..7]

-INSTRD

GND

PD[0..7]

-DIS_FLASH

-WAIT

IICSCL

-RESET

A[0..23]

-IOREQ

PC[0..7]

-CS[0..3]

RTC_VDD

-F91_WP

TDI

TRIGOUT

TCK

TMS

-TRSTN

PA[0..7]

VCC